# XIPHOS Q7

# **Q7** User Manual

Doc No. XSC-1542-6025

April 14th 2020

Submitted To N/A

Xiphos Systems Corporation

Submitted By 3981 boul. St-Laurent, Suite 500

Montréal QC H2W 1Y5

This document is a deliverable under contract no. *INTERNAL*. It contains information proprietary to Xiphos Systems Corporation, or to a third party to which Xiphos Systems Corporation may have legal obligation to protect such information from unauthorized disclosure, use or duplication. Any disclosure, use or duplication of this document or of any of the information contained herein for other than the specific purpose for which it was disclosed is expressly prohibited except as Xiphos Systems Corporation or XIPHOS may otherwise agree to in writing.

## **Product Document Approval**

Title: XIPHOS Q7: Q7 User Manual

XSC Filename: XSC-1542-6025-c Q7RevB User Manual.pdf

Document Type: **Technical Note**Contract Number: **INTERNAL**Submission Date: April 14th 2020

Contact Information: Xiphos Systems Corporation

3981 boul. St-Laurent, Suite 500

Montréal QC H2W 1Y5 email: luq@xiphos.ca tel: 514-847-9474

|                                             | Signature and Date |

|---------------------------------------------|--------------------|

| Product/Document Originator: Lucile Quirion |                    |

|                                             | (signed)           |

|                                             | April 14th 2020    |

|                                             | Signature and Date |

|                                             |                    |

| Product/Document Reviewer: Detlev Casanova  |                    |

|                                             | (signed)           |

|                                             | April 14th 2020    |

## **Contents**

| 1  | Change History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                    |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 2  | Acronyms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6                    |

| 3  | Applicable Documents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7                    |

| 4  | Reference Documents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7                    |

| 5  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8                    |

| 6  | Q7 Overview 6.1 Architecture Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8<br>8<br>10         |

| 7  | <ul> <li>7.1 Electrostatic Discharge Caution</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12                   |

| 8  | Q7S "Space" Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14                   |

| 9  | 9.1 Q7 Radiation Effects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 15<br>16<br>16<br>16 |

| 10 | 10.1 Board Setup10.2 Host workstation configuration10.3 Booting into Linux10.4 Transferring Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16<br>17             |

| 11 | The state of the s | <b>19</b> 19         |

April 14th 2020

Xiphos Document ID: XSC-1542-6025-c, page 2

For more information contact the author directly: luq@xiphos.ca

|    | 11.4<br>11.5<br>11.6<br>11.7                                         | Building the Kernel                  | 20<br>21<br>22<br>22                   |

|----|----------------------------------------------------------------------|--------------------------------------|----------------------------------------|

| 12 | XDI                                                                  | Image Format 2                       | 2                                      |

| 13 | 13.1<br>13.2<br>13.3<br>13.4<br>13.5<br>13.6<br>13.7                 | Partition Layout                     | 23<br>25<br>25<br>26<br>26             |

| 14 |                                                                      | To2Enter U-Boot2Add a root password2 |                                        |

| 15 | 15.1<br>15.2                                                         | ASIC3 Features  Instant-On           | 29                                     |

| 16 | 16.1<br>16.2                                                         | C Design Overview Requirements       | 30                                     |

| 17 | 17.1<br>17.2<br>17.3<br>17.4<br>17.5<br>17.6<br>17.7<br>17.8<br>17.9 | Software Overview                    | 32<br>32<br>33<br>33<br>34<br>34<br>34 |

For more information contact the author directly: luq@xiphos.ca

April 14th 2020

Xiphos Document ID: XSC-1542-6025-c, page 3

|            | 17.11SEM IP (Space) / FPGA Bitstream Scrubbing   |   |   |   |   |   | <br>38 |

|------------|--------------------------------------------------|---|---|---|---|---|--------|

| 18         | 18.1 Control FPGA                                |   |   |   |   |   |        |

|            | 18.2 Processing FPGA                             |   |   |   |   |   |        |

|            | 18.3 Processing FPGA CPU RAM                     |   |   |   |   |   |        |

|            | 18.4 Non-volatile Firmware Storage               |   |   |   |   |   |        |

|            | 18.5 Data Mass Storage                           | • |   | • | • |   | <br>40 |

|            | 18.6 Real Time Clock (RTC)                       | • |   | • |   |   | <br>40 |

| 19         | 19 Q7 Electrical Interfaces                      |   |   |   |   |   | 40     |

|            | 19.1 Power Input Details                         |   |   |   |   |   | <br>41 |

|            | 19.2 Power Consumption                           |   |   |   |   |   | <br>41 |

|            | 19.3 ESD Protection                              |   |   |   |   |   | <br>42 |

|            | 19.4 USB host Current Limit                      |   |   |   |   |   | <br>42 |

|            | 19.5 Mezzanine Connector                         |   |   |   |   |   |        |

| <b>ე</b> ი | 20 Q7 Mechanical Interfaces                      |   |   |   |   |   | 44     |

| 20         | 20.1 Volume                                      |   |   |   |   |   |        |

|            | 20.2 Interface Bolt Pattern and Contact Surfaces |   |   |   |   |   |        |

|            | 20.3 Mass                                        |   |   |   |   |   |        |

|            | 20.4 Thermal Interfaces                          |   |   |   |   |   |        |

|            | 20.5 Q7 Serial Interface                         |   |   |   |   |   |        |

|            | 20.6 Q7 MicroSD                                  |   |   |   |   |   |        |

|            |                                                  |   |   |   |   |   |        |

|            | 20.7 Q7 Connectors                               | • | • | • | • | • | <br>50 |

| 21         | 21 Hardware FAQ                                  |   |   |   |   |   | 52     |

|            | 21.1 U3 PIN 5                                    |   |   |   |   |   | <br>52 |

|            | 21.2 Oxidation                                   |   |   |   |   |   | <br>52 |

|            | 21.3 QFN package pins                            |   |   |   |   |   | <br>52 |

| 22         | 22 Q7-PIM                                        |   |   |   |   |   | 53     |

|            | 22.1 Overview                                    |   |   |   |   |   |        |

|            | 22.2 Real Time clock Battery                     |   |   |   |   |   | 53     |

|            | 22.3 Status LED                                  |   |   |   |   |   | 53     |

|            | 22.4 USB Serial Console                          |   |   |   |   |   | 54     |

|            | 22.5 Multipurpose Connector Pinout               |   |   |   |   |   | 55     |

|            | 22.5 Manupurpose Connector i mout                | • | • | • | • |   | <br>55 |

| 23         | 23 Q7-CameraBoard Information                    |   |   |   |   |   | 57     |

|            | 23.1 Features                                    |   |   |   |   |   | 57     |

April 14th 2020

Xiphos Document ID: XSC-1542-6025-c, page 4

# 1 Change History

| Version | Release Date     | Notes                                        |

|---------|------------------|----------------------------------------------|

| a       | 3 December 2019  | Initial Release.                             |

| b       | 12 February 2020 | Fix Mezzanine connector's pin table          |

| С       | 14 April 2020    | Add remote diagnostic port section           |

|         |                  | Update Building software section (drop eSDK) |

## 2 Acronyms

| ESD | Electrostatic Discharge            | . 11 |

|-----|------------------------------------|------|

|     | Multi-Processor System-on-Chip     |      |

|     | Not OR (electronic logic gate)     |      |

|     | Product Integration Module         |      |

|     | Queued Serial Peripheral Interface |      |

| SEU | Single Event Upset                 | 13   |

|     | Volts Direct Current               |      |

## 3 Applicable Documents

The following documents are considered as an integral part of this document to the extent specified herein.

| Ref | Title | Doc No. | Publisher |  |  |  |  |

|-----|-------|---------|-----------|--|--|--|--|

|     |       |         |           |  |  |  |  |

## 4 Reference Documents

The following documents provide additional information or guidelines that either may clarify the contents or are pertinent to the history of this document.

| Ref Title                                                    | Doc No.                   | Publisher                                |

|--------------------------------------------------------------|---------------------------|------------------------------------------|

| RD01 Q7 Specifications                                       | XTI-2001-2019-<br>d       | XSC                                      |

| RD02 Q7_REV_A_16.6.stp (Step model for the Q7 RevA and RevB) | XSC-1542-0101             | XSC                                      |

| RD03 Q7_PIM_REV_A_10L.stp (Step model for the Q7-PIM)        | XSC-1542-0102             | XSC                                      |

| RD04 Q7-Hardware-Pinout-Customers                            | XSC-1542-<br>6015-a01-flr | XSC                                      |

| RD05 IHLP Standards of Manufacture                           | First Edition 2008        | Vishay Electronics Inductor<br>Divisions |

| RD06 QFN/DFN Inspection of Solder Joints                     | Not available             | Linear Technology Corporation            |

## 5 Introduction

The Q7 is built on the flight and development heritage of the Q4, Q5 and Q6 processors, and is based on a Xilinx Zynq FPGA. Key design objectives for the Q7 included providing a faster CPU, faster RAM and double-precision floating point, while maintaining many of the qualities of the Q6 such as "hybrid" processing, dual SRAM/FLASH FPGA, low power (<1 W) capabilities, and a wide range of available interfaces.

## 6 Q7 Overview

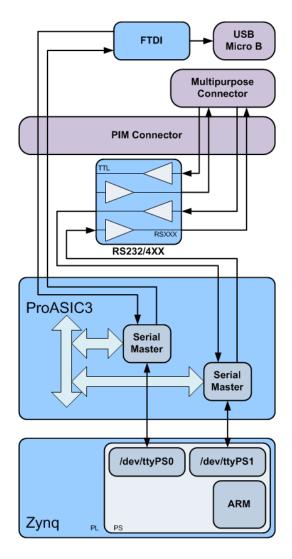

#### 6.1 Architecture Overview

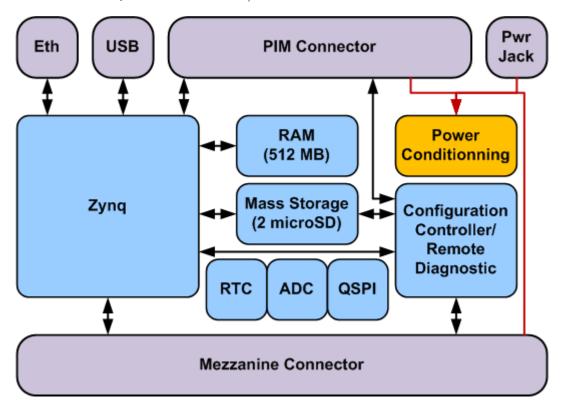

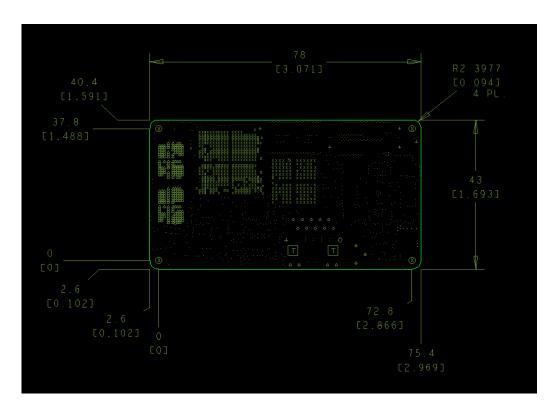

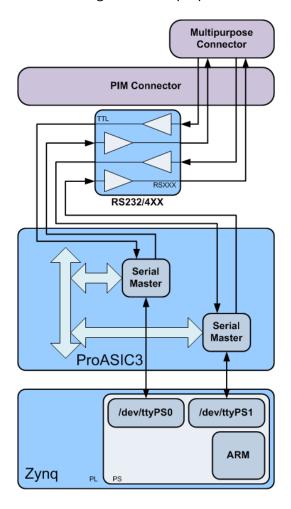

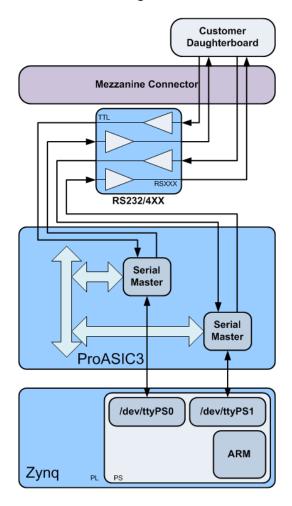

The high-level architecture of the Q7 is presented in the figure below. Details of the interfaces available on the Q7 are presented in the Q7/Interfaces section of this document.

Figure 1: High level architecture

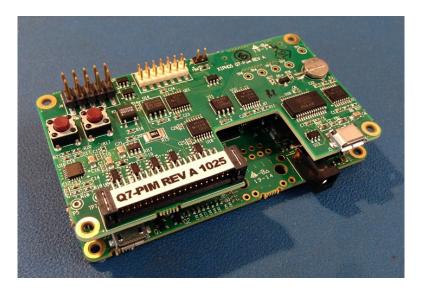

The Q7 is provided with a companion board called the Product Interface Module ("PIM") that is normally included in all sales to new customers. This provides additional features that are not required

April 14th 2020 Xiphos Document ID: XSC-1542-6025-c, page 8

for space missions but that are helpful for development, debugging, and terrestrial applications. Such features include JTAG connectors, power/debug LEDs, RTC battery, a power on/off buttons, CAN, 1-Wire, USB serial console. The image below is of a PIM connected to a Q7.

Figure 2: PIM

The Zynq is the "hybrid" processing FPGA (FPGA + CPU).

It provides the core functionality of the system:

- runs the Linux operating system

- controls the interfaces

- runs application programs, processes data, etc.

- houses the custom application logic

The PA3 is the control FPGA.

It is robust to radiation effects. It is used to implement critical features such as:

- power control

- processing unit Firmware configuration

- remote diagnostic port, and

- watchdog timers.

The Q7 can be "stacked": expansion daughterboards can be directly connected to the Q7. Examples of potential generic daughterboards supported by the Q7 include:

- Basic Board

- 1x wide range input power (5.5mm barrel jack)

- 1x gigabit Ethernet (RJ45 with discrete magnetics)

April 14th 2020

Xiphos Document ID: XSC-1542-6025-c, page 9

For more information contact the author directly: luq@xiphos.ca

- 1x CAN (DB9)

- 1x USB (type A receptacle) master

- USB hub board:

- 1x Wide range input power (5.5mm barrel jack)

- 8x USB connectors (type A receptacle)

- Ethernet Switch board connectors

- 1x Wide range input power (5.5mm barrel jack)

- 4x gigabit Ethernet (RJ45)

- Video board:

- HDMI in

- HDMI out

- Camera Link (MDR26)

- Camera board:

- FireWire (6-pin plug)

- SpaceWire (microDB9)

- Mass storage board

- No connectors

- > 32 GB storage

- > 100 Mbps throughput

## 6.2 Summary of Changes

#### 6.2.1 Hardware

Q7 Rev A and Rev B hardware is identical, with one exception: Rev B has 2x128MB QSPI storage space instead of 2x64MB.

#### 6.2.2 Software

Some Q6 customers have asked us for a summary of changes in software architecture. The design and software interfaces for the core operating system have not changed substantially between Q6 and Q7. Most high-level (i.e. not assembler) language code can be compiled for either platform without any change. For example, most Xiphos-developed Q6 code was compiled for Q7, both kernel and userspace, without any code modification. The following list describes the major differences.

- Boot Loader

- Q6: qboot (Xiphos Proprietary, Limited functionality, < 128kB)</li>

- Q7: u-boot (Open Source, Many Features available, > 128kB)

- Operating System

- Q6: Microblaze Linux 3.12

- Q7 1.x: ARM Linux 4.4

April 14th 2020

Xiphos Document ID: XSC-1542-6025-c, page 10

- Q7 2.x: ARM Linux 4.14

- Userspace (Root filesystem, task management etc.)

- Q6: Buildroot

- Q7 1.x: Yocto 2.1 (krogoth)

- Q7 2.x: Yocto 2.5 (sumo)

- Toolchain:

- Q6: GCC 4.6.4 (single source, Xilinx)

- Q7 1.x: GCC 5.2.1 (Standard Xilinx SDK version 2016.3)

- Q7 2.x: GCC 7.3.0 (Yocto SDK)

- Debug Facilities:

- Q6: Limited. GDB on non-threaded applications sometimes works, no strace.

- Q7: Standard facilities available. strace, gdb. Good threading support.

This document provides the User Manual for Q7 RevB 2.x devices.

Note that on Q7 RevB 2.x devices, Xiphos has introduced the following library:

- LibXiphos which replace userspace tools used to

- boot on another copy

- update the firmware

- writeprotect the NOR Flash

#### 7 Board Overview

## 7.1 Electrostatic Discharge Caution

CAUTION! Electrostatic Discharge (ESD) can damage electronic components when they are improperly handled and can result in total or intermittent failures. Always follow ESD-prevention procedures when removing and replacing components.

Disconnect the power source before moving, cabling, or performing any set up procedures. Inappropriate handling may cause damage to the board.

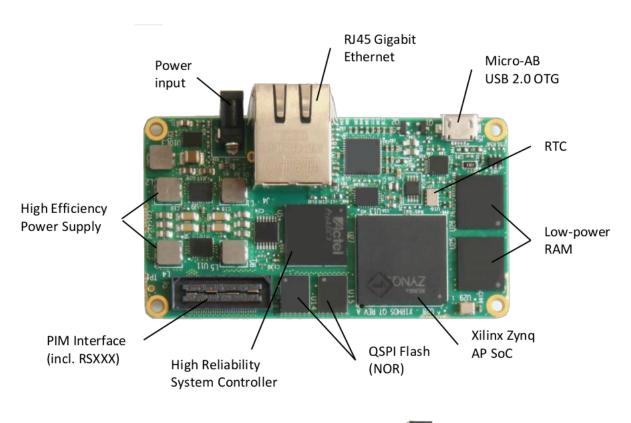

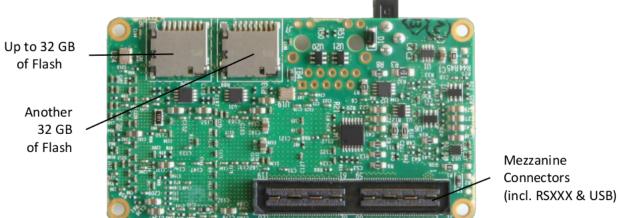

## 7.2 Board Component Location

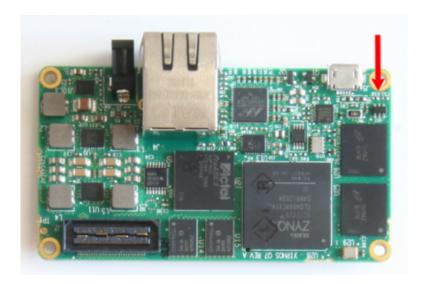

Figure 3: Q7 Board Components

## 7.3 Q7 Robust Design

The Q7 has been designed to provide robustness against radiation effects without using space grade components. The following features have been incorporated in the design:

- Global latch-up detection and protection circuit

- Dedicated MicroSD latch-up detection and protection circuits

- Dual Firmware mass storage chips

- Dual MicroSD cards

- Dual RAM chips

- Use of non-programmable oscillators (programmable oscillators can be damaged by Single Event Upsets (SEUs))

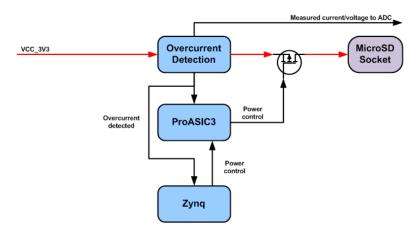

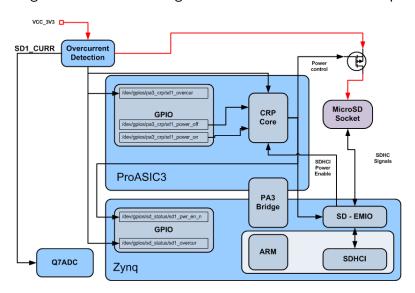

The global latch-up protection circuits detect overcurrent conditions and automatically power cycle the whole Q7 before damage can occur. The current limit is adjustable.

Two dedicated latch-up protection circuits protect the MicroSD against "low current latch-up" that is possible with NAND FLASH controllers. These over-currents are below the global threshold but can damage the MicroSD if not handled properly.

The Zynq firmware (Logic, bootloader, Linux and user applications) is redundantly stored in the two independent mass storage chips. Therefore the Q7 is operational even if one of the two chips is damaged or its contents are corrupted.

Two independent MicroSD cards are present for data storage. They can be used in a redundant way or independently.

Two RAM chips are connected to the Zynq: one to the PS and one to the PL. In normal operation the PL RAM chip is used only as a local buffer for the logic but it can be used by the Zynq processor if the PS RAM chip is damaged.

Programmable oscillators store information in FLASH or EEPROM bits that can flip under radiation. The Q7 uses non-programmable oscillators to prevent this issue.

## 7.4 Q7 Hardware Telemetry

In addition to the robustness features, the following telemetry values are available to monitor the Q7 health:

- Input voltage

- Global current consumption

- MicroSD current consumption

- Zynq die temperature

- PCB temperature

April 14th 2020 Xiphos Docume

For more information contact the author directly: luq@xiphos.ca

Xiphos Document ID: XSC-1542-6025-c, page 13

## 8 Q7S "Space" Features

Xiphos has developed multiple robustness enhancements to handle Single-Event Effects (SEE). These are implemented in the Q7S.

#### 8.0.1 Robust Boot

- Four firmware images are stored in the two 128 MB NOR FLASH devices

- At power-up the ProASIC3 verify image integrity and tries another copy if integrity is compromised

- The boot process is constantly monitored by the ProASIC3, therefore a failed boot is quickly interrupted and the system restarts with a different firmware image

- An integrity check is performed on all code before it is executed

#### 8.0.2 FLASH scrubbing:

- BCH codes are stored in both NOR FLASH devices.

- When requested, the FLASH chips are scrubbed. If an error is present and correctable, it is fixed.

### 8.0.3 Health / error monitoring and logging

Multiple Q7 parameters are automatically logged in a FLASH circular buffer, including:

- Power consumption

- Temperature

- CPU usage

- Input and onboard voltages

A separate circular buffer is used to store various errors, including:

- RAM bit flips

- FLASH bit flips

- Logic configuration bit flips

- Over-temperatures

- Out-of-bounds voltages

- Both buffers are downloaded as part of regular telemetry

### 8.0.4 Watchdog

A dual-level Zynq watchdog (warning/reset) is implemented in the ProASIC3.

## 8.0.5 RAM ECC

Zyng RAM controller and Linux are configured to use ECC on the main memory.

## 8.0.6 Logic Scrubbing

Xilinx SEM IP core is used to detect and correct configuration bit flip errors caused by SEU.

#### 8.0.7 Console logging

A dedicated buffer is present in the ProASIC3 to log the last 8KB of data output from the Q7 debug port. This information can be queried to diagnose software anomalies.

## 9 Q7 Environmental

#### 9.1 Q7 Radiation Effects

Xiphos has flight heritage with the architecture and many components of the Q7. Xiphos has also performed two radiation test campaigns on key components of the Q7 and on the Q7 itself. Test reports are available upon request.

In the public domain, Xilinx has published several papers on radiation induced errors in Series-7 parts at each of the last several IEEE Workshop on Silicon Errors in Logic - Systems Effects (SELSE).

- 2012: Single-Event Effects in 28 Nanometer Configuration and Dual-Port RAM Block Memories

- 2013: Soft Error Study of Memory Cells at 28 Nanometers

- 2014: Soft Error Study of ARM SoC at 28 Nanometers

Detailed reliability information, including radiation cross-section, for all Xilinx components is published with quarterly updates in Xilinx Document UG116, Xilinx Device Reliability Report.

## 9.2 Q7 Thermal Cycling

The Q7 has been formally tested over 200 cycles from -40 to 85°C. Test results are available upon request.

## 9.3 Q7 TVAC

The Q7 has been formally tested for cold and hot start in thermal vacuum. Test results are available upon request.

## 9.4 Q7 Shock & Vibration

The Q7 has been formally tested to shock and vibration targets based on a composite test profile generated by the University of Toronto Institute for Aerospace Studies Space Flight Laboratory.

This encompasses the requirements of the Polar Satellite Launch Vehicle (PSLV), DNEPR, Soyuz-Fregat (in various configurations), and Vega launch vehicles.

Test results are available upon request.

## 10 Quick Start

#### 10.1 Board Setup

The Q7 comes with its firmware installed on Queued Serial Peripheral Interface (QSPI) Not OR (NOR) Flash.

Connect the 6 Volts Direct Current (VDC) power supply.

The Q7 board is now ready to be powered on and off.

## 10.2 Host workstation configuration

For development and testing purpose, we recommend that you use Ubuntu 18.04. The following tools are used for testing purposes: picocom, ssh, etc.

## 10.3 Booting into Linux

Connect the Q7-Product Integration Module (PIM) micro USB port to your host machine.

You can get the port information with:

```

$ dmesg | tail | grep tty

[4749833.015233] usb 1-1.3.4.1: FTDI USB Serial Device converter now attached to

ttyUSB4

```

• Run the following command to start a tty session on the target, press Enter and Login (login: root, no password):

```

$ picocom -b 115200 /dev/ttyUSB4

q7-revb login: root

```

Print firmware version and system information

```

$ cat /etc/os-release

[...]

$ uname -a

[...]

```

## 10.4 Transferring Files

The easiest way to transfer files from/to your workstation is to use the scp command, assuming that the Q7 has a network connection.

Use the following command to verify that the Q7 is connected to the network:

```

$ ip addr show

```

Then from your workstation, copy files to the /tmp directory on target with:

```

$ scp FILE root@${IP_ADDR}:/tmp

```

## 10.5 Enabling USB and SD Cards

To save on power consumption, the Q7 USB port as well as its SD Cards are not powered by default. They must be manually powered in order to use any device connected to them.

April 14th 2020

Xiphos Document ID: XSC-1542-6025-c, page 17

### 10.6 Enabling USB

The USB port is turned ON by using "q7hw" command. The command usage for USB can be shown by typing "q7hw usb help".

Examples for powering ON USB:

```

q7hw usb set on

```

Note that this script is non-blocking (i.e. it does not wait for devices to show up). Any USB device connected will be detected by the kernel and listed at that point (assuming they are supported).

The port can be turned by OFF with the same command:

```

q7hw usb set off

```

## 10.7 Enabling SD Cards

The micro-SD cards are turned ON by using "q7hw" command. The command usage for SD cards can be shown by typing "q7hw sd help".

Examples for powering ON SD cards:

```

# Turning on SD Card 0

q7hw sd set 0 on

# Turning on SD Card 1

q7hw sd set 1 on

# Turning both cards on at once

q7hw sd set all on

# At this point, the card partitions will appear at the path /dev/mmcblk<SDCARD>

p<PARTITION_NUMBER>

# They can be mounted with a command like "mount /dev/mmcblkOp1 /mnt"

```

The card can be turned off with the same commands:

```

# Turning off SD Card 0

q7hw sd set 0 off

# Turning off SD Card 1

q7hw sd set 1 off

# Turning both card off at once

q7hw sd set all off

```

It is safer to unmount the partitions before turning off the SD cards.

Note that the following errors will show up on the console while performing those commands:

## April 14th 2020

Xiphos Document ID: XSC-1542-6025-c, page 18

```

mmc0: Got command interrupt 0x00030000 even though no command operation was in progress.

mmc0: Got command interrupt 0x00030000 even though no command operation was in progress.

mmc0: Got command interrupt 0x00030000 even though no command operation was in progress.

mmc0: Got command interrupt 0x00030000 even though no command operation was in progress.

mmc0: Got command interrupt 0x00030000 even though no command operation was in progress.

```

These lines are normal and are to be expected. They can be safely ignored.

#### 10.8 Persistent Write

#### 10.8.1 Flash

Note that QSPI chips are mounted read-only by default. For applications to be permanently installed on the QSPI or to perform persistent modifications of the root file system, the write protection will have to be disabled during the writes and enabled once the writes have finished.

Please look at the section Writeprotect to understand how to enable or disable the protection. Please look at the section Ugrading the image to see how to update various components. Please look at the section Updating Files to understand how to update files on the root file system.

## 11 Building Software Components

#### 11.1 Prerequisites

This chapter assumes that you are:

- Experienced with embedded software development

- Familiar with ARM architecture

- Familiar with Xilinx development tools such as the Vivado Integrated Design Environment (IDE), the Xilinx software developers kit (SDK), compilers, debuggers, and operating systems.

#### 11.2 Install Yocto SDK

Along with Q-Cards, Xiphos provides a Software Development Kit which enables customers to cross-compile binaries for the Q-card from a Linux Host. First, the SDK has to be installed on a Linux host machine. This is done by running the SDK installation script.

April 14th 2020 Xiphos Document ID: XSC-1542-6025-c, page 19

For more information contact the author directly: luq@xiphos.ca

You can then load the build environment and tools with the following command:

```

source /opt/xiphos/sdk/ark/environment-setup-<ARCH>-xiphos-linux

```

## 11.3 Building the Kernel

#### 11.3.1 Downloading the kernel

The kernel can be downloaded from:

```

https://github.com/XiphosSystemsCorp/linux-xlnx/tree/xiphos-4.14

```

Note that the Xiphos kernel is based on the Xilinx fork of the Linux kernel https://github.com/Xilinx/linux-xlnx

You can use git to download the latest version of the kernel:

```

git clone https://github.com/XiphosSystemsCorp/linux-xlnx.git --branch xiphos -4.14

```

## 11.4 Getting the Kernel Configuration

The kernel configuration may change depending on what the Q-card supports. The easiest way to obtain the correct configuration is to extract it from your Q-card.

To extract this configuration, you must boot your Q-card to its Linux system and type the following command:

```

# On your Q-card

$ zcat /proc/config.gz > /tmp/kernel-config

```

The easiest way to transfer this file to your workstation is to use the scp command, assuming your workstation has SSH and that your Q-card has a network connection.

#### 11.4.1 Preparing the kernel to cross-compile

Before starting the compilation you need to configure the kernel's various configuration options.

April 14th 2020 Xiphos Document ID: XSC-1542-6025-c, page 20

For more information contact the author directly: luq@xiphos.ca

There are several ways to do this. The easiest is to use make menuconfig to bring up the configuration menu.

Note that you MUST have the toolchain installed for this to work; you also need to have its "Development Environment Variables" set up before proceeding. Refer to the article Install Yocto SDK on how to do this.

The following assumes that you used git to clone the kernel in the "linux-xlnx" folder. It also assumes that the kernel configuration copied from the Q-card is now in /tmp/kernel-config on your workstation.

```

# Assuming you installed the SDK in /opt/xiphos/sdk/ark

# Source the SDK environment setup script

$ . /opt/xiphos/sdk/ark/environment-setup-<ARCH>-xiphos-linux

# Assuming you cloned your kernel in linux-xlnx

$ cd linux-xlnx

$ mv /tmp/kernel-config .config

$ make menuconfig

```

You can make the modifications you need in this menu; once you are done, just "Save" your configuration and quit.

#### 11.4.2 Compiling the kernel

Once the configuration is done, you can compile your kernel by using the command:

```

# In the "linux-xlnx" folder you cloned the kernel in make LDFLAGS="" Image

```

If the compilation goes well, an "Image" file will be created.

The Image file is the uncompressed kernel image.

## 11.5 Compiling a Kernel Module

Optionally, you can also build the kernel modules by using the following commands:

```

# Assuming you installed the SDK in /opt/xiphos/sdk/ark

# Source the SDK environment setup script

. /opt/xiphos/sdk/ark/environment-setup-<ARCH>-xiphos-linux

# Force to install the modules in the folder "/tmp/modules" locally

export INSTALL_MOD_PATH=/tmp/modules

# In the "linux-xlnx" folder where you compiled the kernel previously

make LDFLAGS="" modules

make LDFLAGS="" modules_install

```

#### April 14th 2020

Xiphos Document ID: XSC-1542-6025-c, page 21

For more information contact the author directly: luq@xiphos.ca

At this point, the modules will be present in the folder "/tmp/modules".

You can use the following commands to create a modules.tgz file.

```

# Make sure the modules folder match the kernel version

# This assumes the modules are installed in the "modules" local folder

mv custom_modules/lib/modules/4.14.0-xilinx-* modules/lib/modules/4.14.0-xiphos

# Create the .tgz from "modules" local folder

tar -C /tmp/modules -czf modules.tgz .

```

Modules need to be transferred manually to the Q-card, for example by using the Ethernet port.

## 11.6 Compiling Userspace Application Programs

Load the build environment from the SDK (see Install Yocto SDK).

```

# Assuming you installed the SDK in /opt/xiphos/sdk/ark

# Source the SDK environment setup script

$ . /opt/xiphos/sdk/ark/environment-setup-<ARCH>-xiphos-linux

$ make hello_world

```

the application is now ready to be transferred and tested on the Q-card.

## 11.7 Building IP Cores

Refer to Logic Design Overview for information on how to generate and install IP Cores on the Q-card.

## 12 XDI Image Format

A standard Xiphos image file is called a "Xiphos Deployment Image" and has the .xdi file extension. It contains a single copy of the image.

The whole image is a single tar archive, compressed and containing at least the following files:

- A devicetree blob, with a U-Boot header (dtb-xiphos.img),

- A bootable Xilinx firmware (fw.bin), this is the processing unit's entry point. It is composed

of system.bit, fsbl.elf and u-boot.elf package.

- U-boot environment (q7-env.bin)

- Initramfs minimal Linux system (q7-initramfs.img)

- A compressed kernel image file (ulmage),

April 14th 2020 Xiphos Document ID: XSC-1542-6025-c, page 22

For more information contact the author directly: luq@xiphos.ca

A ubi image file (rootfs.ubi) with a single volume containing a ubifs root filesystem.

These files are also added to the XDI image for debugging purpose:

- Xilinx bootloader (fsbl.elf)

- system.bit (Xilinx generated .bit information)

- A U-Boot image (u-boot.elf)

These files can be extracted with the tar command:

```

tar -C /WHERE/TO/EXTRACT -xJf /WHERE/IMAGE/IS.xdi

```

## 13 Upgrading the image

## 13.1 Partition Layout

The Q-card has 128 MB per chip, 256 MB in total. In space configuration, each chip is also divided in two 64 MB parts. There are 2 chips, each with two copies:

- qspi0 nominal

- qspi0 gold

- qspi1 nominal

- qspi1 gold

## 13.2 Manual Boot Selection

To manually force a boot on a specified copy, the tool xsc\_boot\_copy should be used:

It has the following interface:

```

$ xsc_boot_copy -h

Usage: xsc_boot_copy [OPTIONS] [<chip> <copy>]

With 0 arguments return currently booted chip and copy.

With 0 arguments and -r reboot current copy.

With 2 arguments reboot on the specified copy

Possible combinations

0 0 -> qspi0-nom

0 1 -> qspi0-gold

1 0 -> qspi1-nom

1 1 -> qspi1-gold

```

## April 14th 2020

Xiphos Document ID: XSC-1542-6025-c, page 23

For more information contact the author directly: luq@xiphos.ca

```

Options:

-h, --help:

display this message and exit

display the version and exit

-v, --version:

reboot the current copy force boot even if not writeprotected

-r, --reboot:

-f, --force:

-w, --writeprotect: writeprotect before booting

To find out which copy is currently booted, execute the tool with no arguments:

$ xsc_boot_copy

0 0

To reboot on the same copy:

$ xsc_boot_copy -r

re-booting in 3 2 1

To reboot on any copy:

$ xsc_boot_copy 1 0

re-booting in 3 2 1

The tool will first verify that the copy is write-protected. In case it is not, by default, it will print a

warning and abort:

$ writeprotect 0 0 0

[ 271.677153] UBIFS (ubi0:0): background thread "ubifs_bgt0_0" started, PID

$ xsc_boot_copy -r

Warning! Chip 0, copy 0 is unlocked!

By using the "-f" option, the tool can force the reboot anyway.

By using the "-w" option, the tool can writeprotect the target image prior to rebooting:

$ xsc_boot_copy -w 0 0

Warning! Chip 0, copy 0 is unlocked!

[ 422.002492] UBIFS (ubi0:0): background thread "ubifs_bgt0_0" stops

Warning: cannot detach ubi0

It is probably in use

md5: read 4194304 out of 56492032 bytes

md5: read 8388608 out of 56492032 bytes

md5: read 12582912 out of 56492032 bytes

md5: read 16777216 out of 56492032 bytes

md5: read 20971520 out of 56492032 bytes

```

#### April 14th 2020

Xiphos Document ID: XSC-1542-6025-c, page 24

For more information contact the author directly: luq@xiphos.ca

md5:

read

25165824

out of 56492032

bytes

md5:

read

29360128

out of 56492032

bytes

md5:

read

33554432

out of 56492032

bytes

md5:

read

37748736

out of 56492032

bytes

md5:

read

41943040

out of 56492032

bytes

## 13.3 Updating the firmware

Once the Q-card has booted, the XDI file needs to be transferred to the Q-card to be installed (e.g. in /tmp/xsc-image\*.xdi). Once transferred, the flash can be updated using the update\_xdi tool. The user must select:

- bootloader indicating the firmware

- the target NOR chip (0 or 1)

- the target copy to update: 0 for nominal, 1 for gold

- the source XDI file

```

$ update_xdi bootloader 0 0 /tmp/xsc-image*.xdi # This will update the chip 0

nominal firmware.

$ update_xdi bootloader 1 0 /tmp/xsc-image*.xdi # This will update the chip 1

nominal firmware.

$ update_xdi bootloader 0 1 /tmp/xsc-image*.xdi # This will update the chip 0

gold firmware.

$ update_xdi bootloader 1 1 /tmp/xsc-image*.xdi # This will update the chip 1

qold firmware.

```

For more information about update xdi see LibXiphos Tools - update xdi.

## 13.4 Updating the rootfs

Similarly to the firmware, the Linux root flash partition can be updated using the update\_xdi tool.

Note: The rootfs of an active copy cannot be updated. If your Q-card has booted normally, you cannot update rootfs on nominal 0. This operation has to be done from another copy (i.e. nominal 1). More generally, if the target flash partition is attached to an ubi device, that flash partition must first be detached. In this case the update\_xdi tool will exit without performing the update.

```

$ update_xdi rootfs 0 0 /tmp/xsc-image*.xdi # Update the chip 0 nominal rootfs.

$ update_xdi rootfs 1 0 /tmp/xsc-image*.xdi # Update the chip 1 nominal rootfs.

$ update_xdi rootfs 0 1 /tmp/xsc-image*.xdi # Update the chip 0 gold rootfs.

$ update_xdi rootfs 1 1 /tmp/xsc-image*.xdi # Update the chip 1 gold rootfs.

```

For more information about update\_xdi see LibXiphos Tools - update\_xdi.

April 14th 2020 Xiphos Document ID: XSC-1542-6025-c, page 25

For more information contact the author directly: luq@xiphos.ca

### 13.5 Updating the whole image

Running update\_xdi using all will sequentially update a copy completely.

Note: as for the rootfs case, the currently running copy cannot be updated.

```

$ update_xdi all 0 0 /tmp/xsc-image*.xdi # Update the chip 0 nominal copy.

$ update_xdi all 1 0 /tmp/xsc-image*.xdi # Update the chip 1 nominal copy.

$ update_xdi all 0 1 /tmp/xsc-image*.xdi # Update the chip 0 gold copy.

$ update_xdi all 1 1 /tmp/xsc-image*.xdi # Update the chip 1 gold copy.

```

For more information about update\_xdi see LibXiphos Tools - update\_xdi.

## 13.6 Updating the Bitstream, device-tree or kernel

Note: Unlike the rootfs partition case, these files are not in use when Linux is running, since they have been already read completely into memory. As such they can be updated on the flash copy currently booted.

Note: All files can be updated independently but should be done with caution. If unsure, please update all three files using compatible versions.

Example updating the kernel:

```

$ update_xdi kernel 0 0 /tmp/xsc-image*.xdi # Update kernel on chip 0 nominal.

```

Example updating the device-tree:

```

$ update_xdi devicetree 0 0 /tmp/xsc-image*.xdi # Update device-tree on chip 0

nominal.

```

Example updating the logic:

```

$ update_xdi logic 0 0 /tmp/xsc-image*.xdi # Update logic on chip 0 nominal.

```

For more information about update\_xdi see LibXiphos Tools - update\_xdi.

#### 13.7 Updating files

To properly mount a flash copy root partition for writing, these steps must be performed in the correct order:

- 1. Turning off the NOR write protection on that copy only

- 2. Attaching (if not already attached) the MTD to an UBI device

- 3. Creating a mountpoint if necessary, and mounting, or, in case it is mounted already, remounting the UBIFS filesystem as read-write.

April 14th 2020 Xiphos Document ID: XSC-1542-6025-c, page 26

For more information contact the author directly: luq@xiphos.ca

In order to facilitate executing these steps, the xsc\_mount\_copy tool is available.

Example mounting the copy "qspi1-gold":

```

$ xsc_mount_copy 1 1

```

This can be done when booted from any copy, including the one to be mounted.

Then, the user can access the filesystem at the location specified in the output of the tool. Typically: /tmp/mnt < ... > /

Once all the modifications have been performed, it is necessary to reverse the previous steps before rebooting. This is achieved using writeprotect with 1 as the lock argument.

Example locking the copy qspi1-gold

```

$ writeprotect 1 1 1

```

## 13.8 Locking and Unlocking a NOR copy: writeprotect

The writeprotect command can lock/unlock a flash copy:

The flash copy is specified as for the other commands in the first two arguments. The third argument is optional. Without it, the command returns the state of the copy: locked or unlocked. With a third argument set to 0, the command unlocks the flash copy, and with 1 it locks it.

```

$ # Get the state:

$ writeprotect 0 0 # qspi0-nom

$ writeprotect 1 0 # qspi1-nom

$ writeprotect 0 1 # qspi0-gold

$ writeprotect 1 1 # qspi1-gold

$ # Unlock:

$ writeprotect 0 0 0 # qspi0-nom

$ writeprotect 1 0 0 # qspi0-nom

$ writeprotect 0 1 0 # qspi0-gold

$ writeprotect 1 1 0 # qspi1-gold

$ # Lock:

$ writeprotect 0 0 1 # qspi1-nom

$ writeprotect 1 1 1 # qspi1-gold

$ writeprotect 1 1 1 # qspi1-gold

```

The writeprotect command ensures that the rootfs partition is unmounted or remounted read-only before locking the flash, such that any pending operating system cached operations are flushed to the NOR. This may take some time.

April 14th 2020

Xiphos Document ID: XSC-1542-6025-c, page 27

For more information contact the author directly: luq@xiphos.ca

The writeprotect command computes the MD5 hash of the rootfs partition of the specified copy when locking. It then updates the xscinfo partition of the copy with that md5sum. This takes some time.

If the rootfs filesystem is mounted RW, the MD5 of the underlying nor partition changes due to the internal thread of UBIFS. It is required to writeprotect the copy prior to booting or power cycling.

## 14 How To

#### 14.1 Enter U-Boot

Assuming your Q-card is in working order, you can use the following steps to get into U-Boot.

- Connect to the Q-card using your favorite serial terminal tool (e.g., picocom).

- Power cycle (turn off/turn on) your Q-card. You should see u-boot output:

When the prompt "Hit any key to stop autoboot:" appears, hit "space"

Quickly type: run config\_done. You have about 3 seconds for performing all these steps. Restart at step 2 if you missed. The unit is now booted into U-Boot.

#### 14.2 Add a root password

The system supports multiusers and passwords. However the tools to add users, manage groups and passwords are not installed by default.

You can edit the Linux standard file /etc/shadow to change the root password.

The /etc/shadow file stores actual password in encrypted format with additional properties related to the user's password.

## 15 ProASIC3 Features

#### 15.1 Instant-On

The ProASIC3 can be used to provide 'instant-on' functionality for customers' payloads. The device is a ProASIC3-1000 and there is about 50% of the capacity available for mission-specific use. This type of functionality would be managed and integrated by Xiphos with input (as needed) from the customer. Examples of functionality that Xiphos has included are:

- CAN bus communication (CANOpen)

- Radio payload

April 14th 2020 Xiphos Document ID: XSC-1542-6025-c, page 28

For more information contact the author directly: luq@xiphos.ca

- Closed loop thermal control

- Threshold detection/fail-safe triggering

## 15.2 Remote Diagnostic Port

The ProASIC3 provides a remote diagnostic port that can be used to:

- Monitor temperature and power consumption

- Manually configure the Zyng (provide a safe mode)

- Read and write to QSPI FLASH

- Access scratch and circular buffers (if Space functionality is present)

By default the remote diagnostic port is the Q-card RSXXX port, but it can be configured to be connected to any interface used between the Q-card and satellite OBC.

For more information, please refer to the Remote Diagnostic Port section.

## 15.3 Resistance to Single Event Upset (SEU)

The ProASIC3 logic is highly robust against SEU because:

- It is immune to configuration bit upsets

- Logic is compiled in TMR mode

For that reason it is used to implement critical Q-card functionality:

- Zynq robust configuration

- Serial backdoor access for remote diagnostic and firmware update

- Watchdog

It can also be used to implement user's critical code which would not be suited for the Zynq. To do so, custom logic must be designed and compiled. Currently this can only be performed by Xiphos. Therefore, for any customization request, please contact us.

## 16 Logic Design Overview

The Zynq is the Q-card's processing FPGA. It provides the processing and logic resources required to implement mission-specific software and logic.

Custom Zynq logic can be developed by Xiphos from costumers' requirements or directly by customers themselves. This page explains how a user can generate and test logic for the Q-card.

April 14th 2020 Xiphos Document ID: XSC-1542-6025-c, page 29

## 16.1 Requirements

In order to generate custom IP Cores, please refer for instructions to Xilinx Zynq Ultrascale+ Multi-Processor System-on-Chip (MPSoC) & Zynq-7000 AP SoC Design Flow Wiki: https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/18841738/Getting+Started

The Xilinx SDK is free and can be downloaded from the Xilinx website https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/vivado-design-tools/2018-2.html. The Q-card requires Vivado v2018.2. Other versions may work but are not supported by Xiphos.

Building all Q-card boot files requires a Linux host with the following tools:

- The v2018.2 Xilinx SDK (installed with Vivado)

- The devicetree compiler, dtc

- The mkimage tool (from the U-Boot project).

## 16.2 Logic IP Cores Design

Any software or method can be used to design logic IP cores as long as the following criteria are respected:

- If the IP core needs to communicate with the Zynq processor, it must have an AXI slave interface

- If the IP core requires direct Q-card RAM access, it needs an AXI master interface

- If an interrupt line is required, it must follow the Zynq interrupt rules

## 16.3 Generating Q-card files

Xiphos provides customers with a skeleton Vivado project which contains:

- A Vivado project and it's IP Cores

- A constraint file

- Makefiles

- FSBL source code

The Skeleton project is shipped as a zip file and can be extracted with the following command:

```

$ unzip -q ${PROJECT_NAME}_skeleton.zip

$ cd ${PROJECT_NAME}

```

The Vivado project can be generated with the following command:

```

$ source /opt/Xilinx/SDK/2018.2/settings64.sh

$ cd ${PROJECT_NAME}/XilinxVivado/outputs/

$ make project

```

April 14th 2020 Xiphos Document ID: XSC-1542-6025-c, page 30

For more information contact the author directly: luq@xiphos.ca

You should now be able to open the Vivado project file '

```

$ source /opt/Xilinx/SDK/2018.2/settings64.sh

$ cd ${PROJECT_NAME}/XilinxVivado/outputs/

$ make gui

```

Or open \${PROJECT\_NAME}/XilinxVivado/\${PROJECT\_NAME}.xpr with Vivado

After making changes to the project, export the hdf file (including the bitstream) to the outputs directory and run the following command to generate the files

```

$ source /opt/Xilinx/SDK/2018.2/settings64.sh

$ cd ${PROJECT_NAME}/XilinxVivado/outputs/

$ make fw.bin devicetree.img system.bit

$ tar cJf skeleton.xdi fw.bin devicetree.img system.bit

```

The generated skeleton.xdi file can be used to update the bootloader, kernel, logic and devicetree binaries.

We also provide a Makefile within the release archive which can be used to regenerate a full image.xdi

```

# Extract the release archive

$ mkdir ${PROJECT DIR}

$ tar -C ${PROJECT_DIR} -xf xsc-release-[...].tar

$ cd ${PROJECT_DIR}

# Display the makefile usage

$ make help

Usage:

calling `make image.xdi` with no other action will extract

necessary files from the release XDI and rebuild a rootfs

based on the release root filesystem.

If you wish to use your own files when rebuilding the XDI,

simply copy the files in the current directory using the

appropriate name.

- firmware: fw.bin

- devicetree: devicetree.img

- Kernel: Image.gz

- FPGA bitstream: system.bit

If you wish to append custom files to the root filesystem

create a tar.xz archive containing all files with appropriate

paths (see creating userfs.tar.xz below) and run

make USERFS=${YOUR_TAR_FILE}.tar.xz image.xdi

[...]

```

A full step-by-step example to generate a custom 'overlayfs' is provided in the Makefile help. see LibXiphos Tools - update\_xdi for more information on how to install these files on a Q-card.

#### April 14th 2020

Xiphos Document ID: XSC-1542-6025-c, page 31

For more information contact the author directly: luq@xiphos.ca

## 17 Software Features

### 17.1 Software Overview

The following list describes the major software components:

- Boot Loader: Based on Xilinx U-boot

- Linux Kernel: Based on Xilinx Linux 2018.02 (Linux 4.14 LTS)

- Operating System: Yocto 2.5 (sumo)

- busybox, executable which provides many common UNIX utilities

- systemd, init system and system processes manager

- Toolchain: GCC 7.3.0 (Yocto sumo SDK)

- PA3 programmable logic: Custom

- Zyng programmable logic: Custom

#### 17.2 Features Overview

The Q-card comes in two different flavors: ground (the default) and space.

For convenience purposes, we try to make the space configuration a superset of the ground configuration. This means that it has everything the ground configuration provides plus extra features.

The default configuration includes:

- A robust boot and application watchdog,

- A fallback mechanism implemented via:

- Two redundant firmware images,

- Firmware image data corruption detection code,

- A robust firmware update mechanism.

The extra features include:

- Four redundant firmware images,

- A remote diagnostic port,

- Triple-mode redundancy in the PA3 logic,

- ECC'd RAM,

- A SEM-IP core,

- A Safe Mode.

- A UART buffer.

- A scratch buffer, and

- QSPI FLASH scrubbing (available on demand), and

- RAM scrubbing (available on demand).

April 14th 2020

Xiphos Document ID: XSC-1542-6025-c, page 32

## 17.3 Watchdog

The Q-card provides a software watchdog implemented in the ProASIC3 logic. If it detects a software hang-up or other abnormal behaviour it reboots the Q-card.

The Zyng watchdog is a feature implemented by:

- the ProASIC3 logic,

- a generic Linux kernel driver developed by Xiphos,

- and the standard Linux kernel watchdog API.

This standard Linux kernel watchdog API usable from user-space is described in:

/Documentation/watchdog/watchdog-api.txt.

Watchdog duration is user selectable between 0.001 and 171 seconds.

The watchdog device file is name /dev/xsc\_logic\_wdt\_v1\_0.

You can use libxiphos to programmatically enable/disable the watchdog and set the nowayout feature.

#### 17.4 Hibernate

/dev/rtc0 is the hardware RTC which interfaces to the Q-card via I2C.

You can use standard tools to test the hardware RTC:

```

# synchronize the HARDWARE clock with system clock

/sbin/hwclock -w -f /dev/rtc0

# shut down system and wake up from hibernate in 10 seconds

/usr/sbin/rtcwake -u -d /dev/rtc0 -s10 --mode off

```

#### 17.5 Fallback mechanism

The integrity of the images is verified during the boot process via CRC and md5sum.

This ensures the detection of firmware image data corruption, and makes it possible to boot on a safe firmware image.

### 17.6 Robust Firmware Upgrade Mechanism

The Q-card provides an application that can upgrade partial or complete firmware images.

April 14th 2020

Xiphos Document ID: XSC-1542-6025-c, page 33

### 17.6.1 LibXiphos update\_xdi

The update\_xdi tool is able to update a Q-card flash copy, using an XDI image as the source.

The tool has the following interface:

The tool performs the following actions:

- 1. First the tool verifies that the needed components can be found in the specified xdi file.

- 2. Second, the tool makes sure that the flash copy is unlocked properly, as needed before the operation.

- 3. Third, the tool prepares the target device: for partitions it erases them, and for files, it attaches (UBI) and mounts the target rootfs partition.

- 4. Fourth, the tool writes the file to the device.

- 5. Lastly, the tool unmounts the rootfs partition, or remounts it read-only, detaches the UBI from the MTD if possible, and write-protects the NOR chip: computing the checksum of the rootfs, and then locking the flash chip.

## 17.7 Triple-mode redundancy (Space)

Q-card Space ProASIC3 logic is synthesized with TMR to protect it against SEU.

## 17.8 RAM ECC (Space)

The Q-card Space has ECC protection on RAM which mitigates temporary and permanent bit flips due to radiation effects.

## 17.9 Safe Mode (Space / Mission Specific)

The Q-card Space can halt its boot process until it receives commands through its backdoor interface. This Safe Mode feature is required to prevent boot loop or boot crashes on remote environments.

April 14th 2020 Xiphos Document ID: XSC-1542-6025-c, page 34

For more information contact the author directly: luq@xiphos.ca

This is a factory configurable mode into which the Q-card Space goes once power is applied or the PA3 is reset. In safe mode:

- The Zyng is kept in reset

- Backdoor access is possible

- A command to boot can be received by the ProASIC3

## 17.10 Remote Diagnostic Port (Space)

The Q-Card Space has a remote diagnostic port (RDP) in the ProASIC3 that can be used to perform operations if the boot process fails.

The port allows the user to:

- Read and Write to QSPI Flash

- Manually configure the Zynq

- Monitor temperature and power consumption

- Access scratch and circular buffer

The remote diagnostic port is usually connected to the satellite main OBC.

It can also be connected directly to a radio.

Although the RDP is not required for proper Q-card operation it is highly recommended to implement one in the satellite system: it provides a backdoor to access the Q-card even when everything else is not working.

Note: The remote diagnostic port access to NOR FLASH and telemetry is not functional if the Q-Card Xilinx FPGA is configured.

#### 17.10.1 Default Communication Interface

The base version of the RDP uses a UART interface with the following characteristics:

Baud rate: 115200 bps

Data bits: 8Parity: NoStop bits: 1Duplex: Full

The RDP can also be configured for half-duplex operation. If this option is required, please contact XSC.

A custom packet protocol is implemented on top of the UART. To abstract the communication layer, XSC provides a C library that can be used by customers to add the functionality to their application running on some computer other than the Q-Card, for example on the satellite OBC.

April 14th 2020 Xiphos Document ID: XSC-1542-6025-c, page 35

For more information contact the author directly: luq@xiphos.ca

The RDP can be independent or shared with another UART connected to the Xilinx FPGA. The Q-Card default configuration shares the RDP with the Zynq PS0 UART.

By default the RDP is in bypass mode and does not interfere with regular communications untils it detects a 250ms or more "break" signal (standard signal for UART). Once the signal is detected, it will start to listen on the port and interpret incoming data. Once the communication with the RDP is not required anymore it can be returned to the bypass mode.

If the "break" signal cannot be implemented by the customer application, please contact XSC for alternative methods.

#### 17.10.2 Software Tools

The following sections assumes that the default communication interface is used.

#### 17.10.3 Library