# VA10800/VA10820 ARM<sup>®</sup> Cortex<sup>®</sup>-M0 based Processor Programmers Guide

Nov 2018 Version 1.19

# VA10800/VA10820

# VA10800/VA10820 Programmers Guide

### 1 Overview

This document describes the programmer's view of the VORAGO VA10800/VA10820 ARM<sup>®</sup> Cortex<sup>®</sup>-M0 based microcontrollers.

### 1.1 Related Documents

- ARM<sup>®</sup> Documents (Available from <a href="http://infocenter.arm.com">http://infocenter.arm.com</a>)

- Cortex<sup>®</sup>-M0 Generic User Guide

- Cortex<sup>®</sup>-M0 Technical Reference Manual

- AMBA<sup>®</sup> 3 AHB-Lite Protocol Specification

- AMBA<sup>®</sup> 3 APB Protocol Specification

- NXP Documents (Available from <a href="http://www.nxp.com">http://www.nxp.com</a>)

- o I<sup>2</sup>C-bus specification and user manual

- IEEE

- 1149.1-2013 IEEE Standard for Test Access Port and Boundary-Scan Architecture

- VORAGO Documents

- o VA10800/VA10820 Data Sheet

# VA10800/VA10820

### Contents

| 1 | Ove  | erview | /                                                        | 1         |

|---|------|--------|----------------------------------------------------------|-----------|

|   | 1.1  | Rela   | ted Documents                                            | 1         |

| 2 | Fund | ctiona | I Description                                            | 8         |

|   | 2.1  | Feat   | ures                                                     | 8         |

|   | 2.2  | Bloc   | k Diagram 1                                              | 2         |

|   | 2.3  | Men    | nory Map 1                                               | 3         |

|   | 2.4  | Pow    | er-Up Sequence                                           | 3         |

|   | 2.4. | 1      | Power-Up and Reset Behavior of pins1                     | 4         |

|   | 2.5  | Othe   | er Resets 1                                              | 5         |

|   | 2.6  | l²C p  | pins 1                                                   | 5         |

| 3 | AR۸  | A® Co  | prtex <sup>®</sup> -M0 processor                         | 6         |

| 4 | Peri | phero  | als1                                                     | 7         |

|   | 4.1  | Syste  | em Configuration Peripheral (Software label = SYSCONFIG) | 7         |

|   | 4.1. | 1      | RST_STAT Register 1                                      | 9         |

|   | 4.1. | 2      | RST_CNTL_ROM Register 1                                  | 9         |

|   | 4.1. | 3      | RST_CNTL_RAM Register 1                                  | 9         |

|   | 4.1. | 4      | ROM_PROT Register                                        | 20        |

|   | 4.1. | 5      | ROM_SCRUB Register                                       | 20        |

|   | 4.1. | 6      | RAM_SCRUB Register                                       | 20        |

|   | 4.1. | 7      | ROM_TRAP_ADDR Register                                   | 21        |

|   | 4.1. | 8      | ROM_TRAP_SYND Register                                   | 21        |

|   | 4.1. | 9      | RAM_TRAP_ADDR Register                                   | 22        |

|   | 4.1. | 10     | RAM_TRAP_SYND Register                                   | 22        |

|   | 4.1. | 11     | IRQ_ENB Register                                         | 22        |

|   | 4.1. | 12     | IRQ_RAW Register                                         | <u>23</u> |

|   | 4.1. | 13     | IRQ_END Register                                         | <u>23</u> |

|   | 4.1. | 14     | IRQ_CLR Register                                         | <u>23</u> |

|   | 4.1. | 15     | RAM_SBE Register                                         | 24        |

|   | 4.1. | 16     | RAM_MBE Register                                         | 24        |

|     | 4.1.17                                                                                                      | ROM_SBE Register                                                                                                                                                                                                                                                                                                                                                                             | 24                                                                                                                                             |

|-----|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 4.1.18                                                                                                      | ROM_MBE Register                                                                                                                                                                                                                                                                                                                                                                             | 24                                                                                                                                             |

|     | 4.1.19                                                                                                      | IOCONFIG_CLKDIV0-7 Registers                                                                                                                                                                                                                                                                                                                                                                 | 25                                                                                                                                             |

|     | 4.1.20                                                                                                      | ROM_RETRIES Register                                                                                                                                                                                                                                                                                                                                                                         | 25                                                                                                                                             |

|     | 4.1.21                                                                                                      | REFRESH_CONFIG Register                                                                                                                                                                                                                                                                                                                                                                      | 25                                                                                                                                             |

|     | 4.1.22                                                                                                      | TIM_RESET Register                                                                                                                                                                                                                                                                                                                                                                           | 26                                                                                                                                             |

|     | 4.1.23                                                                                                      | TIM_CLK_ENABLE Register                                                                                                                                                                                                                                                                                                                                                                      | 26                                                                                                                                             |

|     | 4.1.24                                                                                                      | PERIPHERAL_RESET Register                                                                                                                                                                                                                                                                                                                                                                    | 26                                                                                                                                             |

|     | 4.1.25                                                                                                      | PERIPHERAL_CLK_ENABLE Register                                                                                                                                                                                                                                                                                                                                                               | 27                                                                                                                                             |

|     | 4.1.26                                                                                                      | Lockup Reset Register                                                                                                                                                                                                                                                                                                                                                                        | 28                                                                                                                                             |

|     | 4.1.27                                                                                                      | EF_CONFIG Register                                                                                                                                                                                                                                                                                                                                                                           | 28                                                                                                                                             |

|     | 4.1.28                                                                                                      | EF_ID Register                                                                                                                                                                                                                                                                                                                                                                               | 29                                                                                                                                             |

|     | 4.1.29                                                                                                      | PROCID Register                                                                                                                                                                                                                                                                                                                                                                              | 30                                                                                                                                             |

|     | 4.1.30                                                                                                      | PERID Register                                                                                                                                                                                                                                                                                                                                                                               | 30                                                                                                                                             |

| 4.  | 2 IRQ                                                                                                       | Selector Peripheral (Software label = IRQSEL)                                                                                                                                                                                                                                                                                                                                                | 31                                                                                                                                             |

| ••• |                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                |

|     | 4.2.1                                                                                                       | Interrupt Select Register                                                                                                                                                                                                                                                                                                                                                                    | 34                                                                                                                                             |

|     |                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                |

|     | 4.2.1                                                                                                       | Interrupt Select Register                                                                                                                                                                                                                                                                                                                                                                    | 35                                                                                                                                             |

| 4.  | 4.2.1<br>4.2.2<br>4.2.3                                                                                     | Interrupt Select Register                                                                                                                                                                                                                                                                                                                                                                    | 35<br>35                                                                                                                                       |

|     | 4.2.1<br>4.2.2<br>4.2.3                                                                                     | Interrupt Select Register<br>Interrupt Status Register<br>PERID Register                                                                                                                                                                                                                                                                                                                     | 35<br>35<br>36                                                                                                                                 |

|     | 4.2.1<br>4.2.2<br>4.2.3<br>3 IO 0                                                                           | Interrupt Select Register<br>Interrupt Status Register<br>PERID Register<br>Configuration Peripheral (Software label = IOCONFIG)                                                                                                                                                                                                                                                             | 35<br>35<br>36<br>38                                                                                                                           |

|     | 4.2.1<br>4.2.2<br>4.2.3<br>3 IO (<br>4.3.1                                                                  | Interrupt Select Register<br>Interrupt Status Register<br>PERID Register<br>Configuration Peripheral (Software label = IOCONFIG)<br>IO Configuration Register                                                                                                                                                                                                                                | 35<br>35<br>36<br>38<br>39                                                                                                                     |

|     | 4.2.1<br>4.2.2<br>4.2.3<br>3 IO (<br>4.3.1<br>4.3.2                                                         | Interrupt Select Register<br>Interrupt Status Register<br>PERID Register<br>Configuration Peripheral (Software label = IOCONFIG)<br>IO Configuration Register<br>Loopback Mode                                                                                                                                                                                                               | 35<br>35<br>36<br>38<br>39<br>39                                                                                                               |

|     | 4.2.1<br>4.2.2<br>4.2.3<br>3 IO (<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4                                       | Interrupt Select Register<br>Interrupt Status Register<br>PERID Register<br>Configuration Peripheral (Software label = IOCONFIG)<br>IO Configuration Register<br>Loopback Mode<br>Function Selections                                                                                                                                                                                        | 35<br>35<br>36<br>38<br>39<br>39<br>41                                                                                                         |

| 4.  | 4.2.1<br>4.2.2<br>4.2.3<br>3 IO (<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4                                       | Interrupt Select Register<br>Interrupt Status Register<br>PERID Register<br>Configuration Peripheral (Software label = IOCONFIG)<br>IO Configuration Register<br>Loopback Mode<br>Function Selections<br>PERID Register                                                                                                                                                                      | 35<br>35<br>36<br>38<br>39<br>39<br>41<br>42                                                                                                   |

| 4.  | 4.2.1<br>4.2.2<br>4.2.3<br>3 IO (<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4 Utili                            | Interrupt Select Register<br>Interrupt Status Register<br>PERID Register<br>Configuration Peripheral (Software label = IOCONFIG)<br>IO Configuration Register<br>Loopback Mode<br>Function Selections<br>PERID Register<br>ty Peripheral (Software label = UTILITY)                                                                                                                          | <ol> <li>35</li> <li>35</li> <li>36</li> <li>38</li> <li>39</li> <li>39</li> <li>41</li> <li>42</li> <li>44</li> </ol>                         |

| 4.  | 4.2.1<br>4.2.2<br>4.2.3<br>3 IO (<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4 Utili<br>4.4.1                   | Interrupt Select Register<br>Interrupt Status Register<br>PERID Register<br>Configuration Peripheral (Software label = IOCONFIG)<br>IO Configuration Register<br>Loopback Mode<br>Function Selections<br>PERID Register<br>ty Peripheral (Software label = UTILITY)<br>SYND_DATA0/SYND_DATA1/SYND_SYND Registers                                                                             | <ul> <li>35</li> <li>35</li> <li>36</li> <li>38</li> <li>39</li> <li>39</li> <li>41</li> <li>42</li> <li>44</li> <li>44</li> </ul>             |

| 4.  | 4.2.1<br>4.2.2<br>4.2.3<br>3 IO (<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4 Utili<br>4.4.1<br>4.4.2          | Interrupt Select Register<br>Interrupt Status Register<br>PERID Register<br>Configuration Peripheral (Software label = IOCONFIG)<br>IO Configuration Register<br>Loopback Mode<br>Function Selections<br>PERID Register<br>ty Peripheral (Software label = UTILITY)                                                                                                                          | <ul> <li>35</li> <li>35</li> <li>36</li> <li>38</li> <li>39</li> <li>39</li> <li>41</li> <li>42</li> <li>44</li> <li>44</li> <li>44</li> </ul> |

| 4.  | 4.2.1<br>4.2.2<br>4.2.3<br>3 IO (<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4 Utili<br>4.4.1<br>4.4.2<br>4.4.3 | Interrupt Select Register<br>Interrupt Status Register<br>PERID Register<br>Configuration Peripheral (Software label = IOCONFIG)<br>IO Configuration Register<br>Loopback Mode<br>Function Selections<br>PERID Register<br>ty Peripheral (Software label = UTILITY)<br>SYND_DATA0/SYND_DATA1/SYND_SYND Registers<br>SYND_ENC_32 Registers<br>SYND_CHECK_32_DATA/SYND_CHECK_32_SYND Registers | <ol> <li>35</li> <li>36</li> <li>38</li> <li>39</li> <li>41</li> <li>42</li> <li>44</li> <li>44</li> <li>45</li> </ol>                         |

| 4.4.7   | SYND_CHECK_32_52_DATA/SYND_CHECK_32_52_SYND Registers | . 46 |

|---------|-------------------------------------------------------|------|

| 4.4.8   | PERID Register                                        | . 47 |

| 4.5 Ger | neral Purpose IO Peripheral (Software label = GPIO)   | . 48 |

| 4.5.1   | DATAIN Register                                       | . 50 |

| 4.5.2   | DATAINRAW Register                                    | . 50 |

| 4.5.3   | DATAOUT Register                                      | . 51 |

| 4.5.4   | DATAOUTRAW Register                                   | . 51 |

| 4.5.5   | SETOUT Register                                       | . 51 |

| 4.5.6   | CLROUT Register                                       | . 51 |

| 4.5.7   | TOGOUT Register                                       | . 52 |

| 4.5.8   | DATAMASK Register                                     | . 52 |

| 4.5.9   | DIR Register                                          | . 52 |

| 4.5.10  | PULSE Register                                        | . 52 |

| 4.5.11  | PULSEBASE Register                                    | . 53 |

| 4.5.12  | DELAY1 and DELAY2 Registers                           | . 53 |

| 4.5.13  | IRQ_SEN, IRQ_EDGE, and IRQ_EVT Registers              | . 53 |

| 4.5.14  | IRQ_ENB Register                                      | . 55 |

| 4.5.15  | IRQ_RAW Register                                      | . 55 |

| 4.5.16  | IRQ_END Register                                      | . 56 |

| 4.5.17  | EDGE_STATUS Register                                  | . 56 |

| 4.5.18  | PERID Register                                        | . 56 |

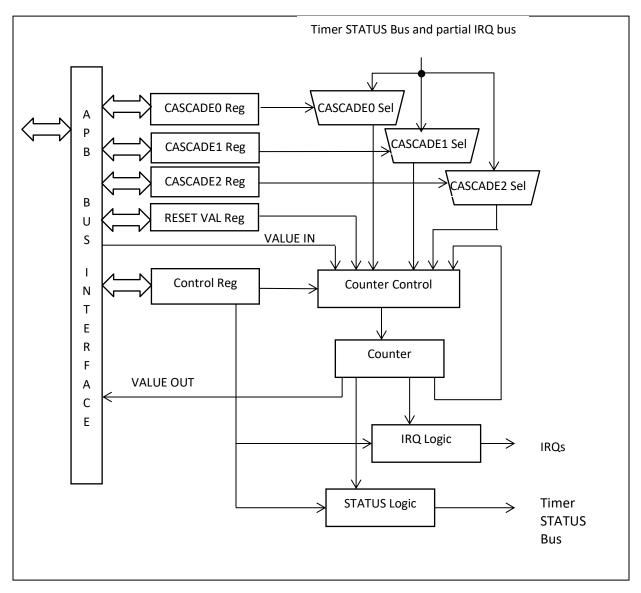

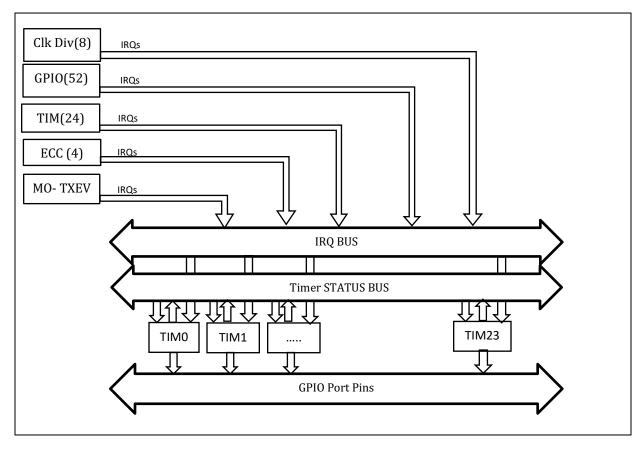

| 4.6 Tim | er/Counter Peripheral (Software label = TIMER)        | . 57 |

| 4.6.1   | CTRL Register                                         | . 60 |

| 4.6.2   | RST_VALUE Register                                    | . 63 |

| 4.6.3   | CNT_VALUE Register                                    | . 63 |

| 4.6.4   | ENABLE Register                                       | . 63 |

| 4.6.5   | CSD_CTRL Register                                     | . 64 |

| 4.6.6   | CASCADE0, CASCADE1, and CASCADE2 Register             | . 65 |

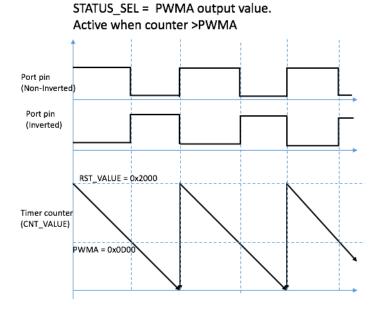

| 4.6.7   | PWMA_VALUE Register                                   | . 67 |

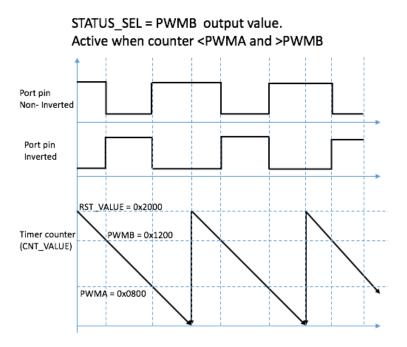

| 4.6.8   | PWMB_VALUE Register                                   | . 67 |

| 4.6.9   | PERID Register                                  | 68 |

|---------|-------------------------------------------------|----|

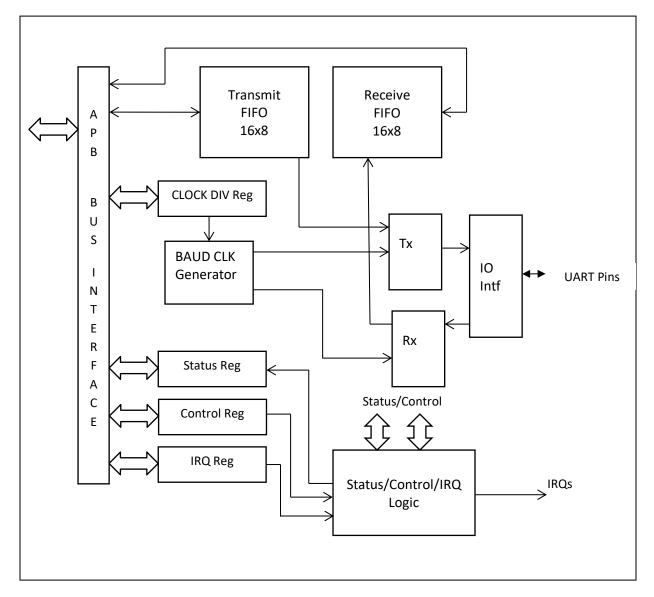

| 4.7 UAI | RT Peripheral (Software label = UARTA & UARTB)  | 69 |

| 4.7.1   | UART Transactions                               | 71 |

| 4.7.2   | DATA Register                                   | 72 |

| 4.7.3   | ENABLE Register                                 | 72 |

| 4.7.4   | CTRL Register                                   | 72 |

| 4.7.5   | CLKSCALE Register                               | 74 |

| 4.7.6   | RXSTATUS Register                               | 75 |

| 4.7.7   | TXSTATUS Register                               | 76 |

| 4.7.8   | FIFO_CLR Register                               | 76 |

| 4.7.9   | TXBREAK Register                                | 76 |

| 4.7.10  | ADDR9 Register                                  | 77 |

| 4.7.11  | ADDR9MASK Register                              | 78 |

| 4.7.12  | IRQ_ENB Enable Register                         | 78 |

| 4.7.13  | IRQ_RAW Register                                | 79 |

| 4.7.14  | IRQ_END Register                                | 79 |

| 4.7.15  | IRQ_CLR Register                                | 79 |

| 4.7.16  | RXFIFOIRQTRG Register                           | 79 |

| 4.7.17  | TXFIFOIRQTRG Register                           | 79 |

| 4.7.18  | RXFIFORTSTRG Register                           | 79 |

| 4.7.19  | STATE Register                                  | 80 |

| 4.7.20  | PERID Register                                  | 80 |

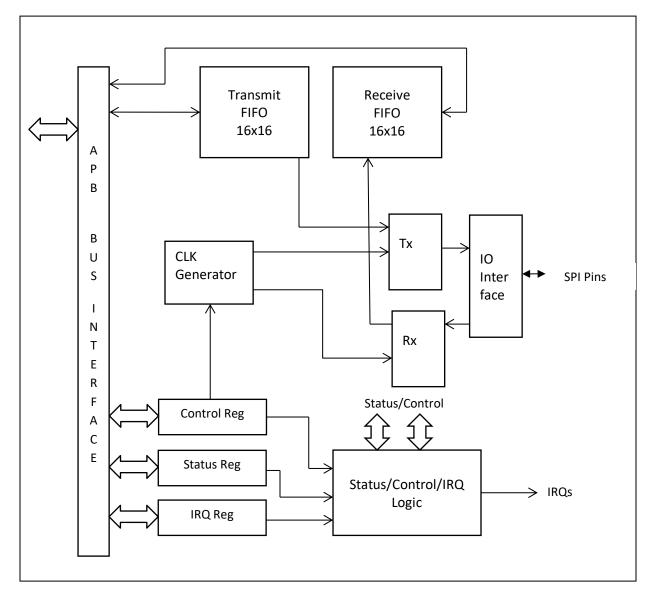

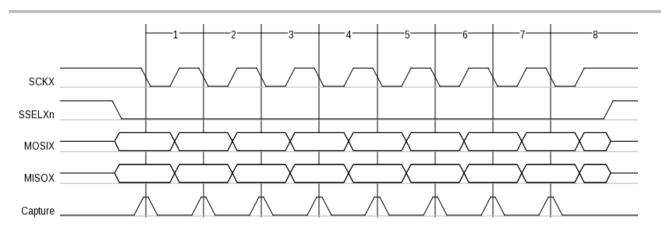

| 4.8 SPI | Peripheral (Software label = SPIA, SPIB & SPIC) | 81 |

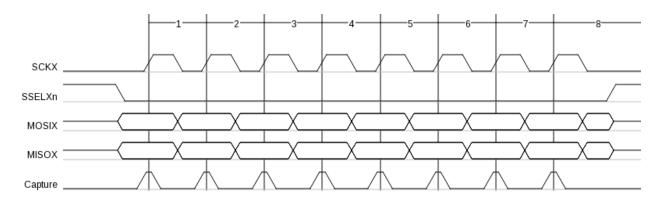

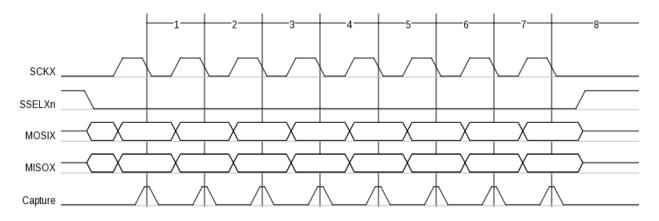

| 4.8.1   | SPI Transactions                                | 83 |

| 4.8.2   | CTRLO Register                                  | 84 |

| 4.8.3   | CTRL1Register                                   | 86 |

| 4.8.4   | DATA Register                                   | 88 |

| 4.8.5   | STATUS Register                                 | 88 |

| 4.8.6   | CLKPRESCALE Register                            | 89 |

| 4.8.7   | IRQ_ENB Register                                | 89 |

|   | 4.8.8                | IRQ_RAW Register                            |

|---|----------------------|---------------------------------------------|

|   | 4.8.9                | IRQ_END Register                            |

|   | 4.8.10               | IRQ_CLR Register                            |

|   | 4.8.11               | RXFIFOIRQTRG Register                       |

|   | 4.8.12               | TXFIFOIRQTRG Register                       |

|   | 4.8.13               | FIFO_CLR Register                           |

|   | 4.8.14               | STATE Register                              |

|   | 4.8.15               | PERID Register                              |

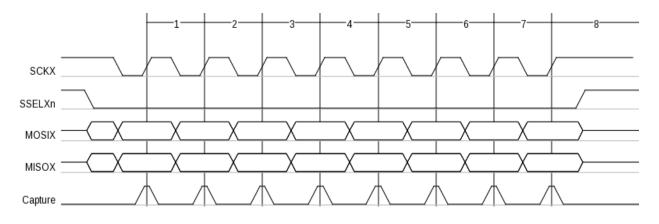

| 4 | 4.9 l <sup>2</sup> C | Peripheral (Software label = I2CA and I2CB) |

|   | 4.9.1                | I <sup>2</sup> C Master Transactions        |

|   | 4.9.2                | I <sup>2</sup> C Master Registers           |

|   | 4.9.3                | I <sup>2</sup> C Slave Registers            |

|   | 4.9.4                | PERID Register                              |

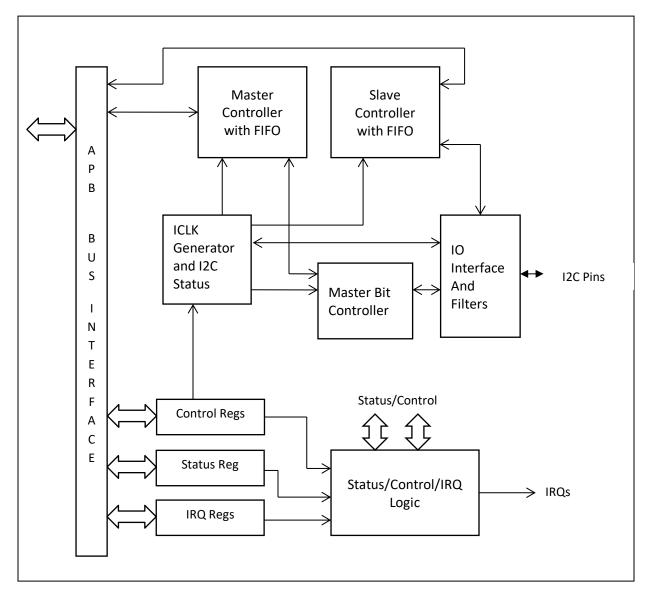

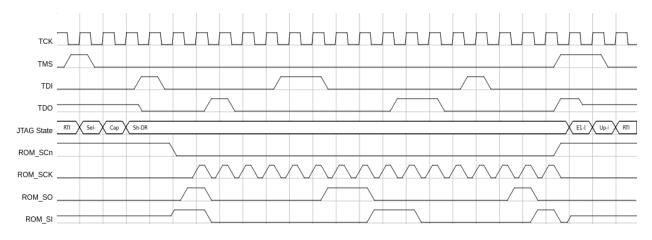

| 5 | JTAG co              | ntroller and eFuse block                    |

| 2 | 5.1 ARA              | M® Cortex®-M0 JTAG Controller               |

|   | 5.1.1                | Instruction Codes                           |

| 2 | 5.2 Chip             | b Level JTAG Controller                     |

|   | 5.2.1                | Instruction Codes                           |

|   | 5.2.2                | BOOT_CFG Register 115                       |

|   | 5.2.3                | RESET_CFG Register 117                      |

|   | 5.2.4                | EF_ADDR Register                            |

|   | 5.2.5                | EF_WDATA Register                           |

|   | 5.2.6                | EF_RDATA Register                           |

|   | 5.2.7                | EF_CMD Register                             |

|   | 5.2.8                | EF_STATUS Register 118                      |

|   | 5.2.9                | EF_TIMING Register                          |

|   | 5.2.10               | SPI_CONFIG Register                         |

|   | 5.2.11               | SPI_ENCAP Register                          |

|   | 5.2.1                | HBO_CMD Register 120                        |

|   | 5.2.2                | HBO_STATUS Register                         |

|   | 5.3  | eFuse                                      |

|---|------|--------------------------------------------|

|   | 5.3. | 1 eFuse read procedure                     |

|   | 5.3. | 2 eFuse write procedure                    |

|   | 5.3. | 3 Sample eFuse first time write procedure  |

|   | 5.3. | 4 Sample eFuse second time write procedure |

| 6 | Port | ing Notes                                  |

|   | 6.1  | Memory System                              |

|   | 6.2  | System Configuration Peripheral            |

|   | 6.3  | IRQ Selector Peripheral                    |

|   | 6.4  | IO Configuration Peripheral                |

|   | 6.5  | Utility Peripheral                         |

|   | 6.6  | External Memory Peripheral 126             |

|   | 6.7  | General Purpose IO Peripheral              |

|   | 6.8  | Timer/Counter Peripheral                   |

|   | 6.9  | UART Peripheral                            |

|   | 6.10 | SPI Peripheral                             |

|   | 6.11 | I <sup>2</sup> C Peripheral                |

| 7 | Revi | sion History                               |

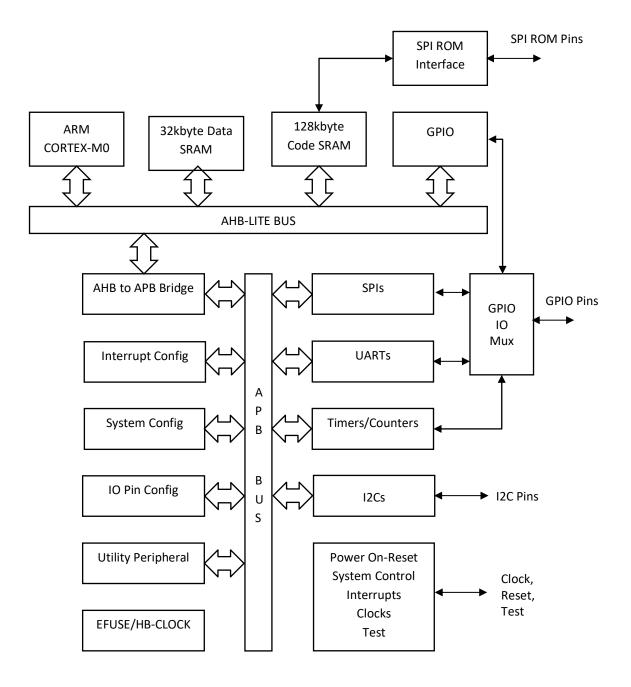

### 2 Functional Description

The VA10800 and VA10820 MCUs contains an ARM<sup>®</sup> Cortex<sup>®</sup>-M0 processor, and a related set of peripherals.

### 2.1 Features

- Processor Core

- ARM<sup>®</sup> Cortex<sup>®</sup>-M0 processor

- Up to 50 MHz

- SysTick Counter

- Single Cycle Multiply

- ARM<sup>®</sup> Cortex<sup>®</sup>-M0 built-in Nested Vectored Interrupt Controller (NVIC)

- 32 Interrupt sources with unique priority level

- Tail chaining supported

- CoreSight<sup>™</sup> compliant debug access via JTAG based Debug interface

- 4 Breakpoint Comparators

- 2 Data Watch Point Comparators

- JTAG Debug Port

- Memory

- 32kbyte Data Memory

- 128kbyte Code Memory

- Loaded from external Serial Peripheral Interface (SPI) based memory at startup

- Configurable boot delay, boot speed, and boot checking

- Byte level Error Correct and Detect (EDAC) logic (VA10820 Only)

- Scrub Engine (VA10820 Only)

- Peripherals

- o 2 UARTs

- 16 word Transmit and Receive FIFOs

- Fractional baud rate generation

- Supports baud rates up to 115200 with system clocks above 2MHz

- Supports 5, 6, 7, 8 and 9 bits

- Supports Even, Odd, and No parity

- Stop Bits 1 or 2

- Supports Break generation and detection

- Error detection

- FIFO overflow

- Framing error

- Parity error

- Break detection

- Configurable Interrupt generation

- FIFO level (fully configurable)

- Receive Timeout

- Error

- 3 SPI Ports (One is designated Master only)

- Supports all 4 modes of Motorola's SPI Specification

- Word/Frame size of 4 to 16 bits

- 16 word Transmit and Receive FIFOs

- Block mode support for larger Frame sizes

- Master mode rates up to 1/4 the system clock

- Slave mode rates up to 1/12 the system clock

- Configurable Interrupt generation

- FIFO level (fully configurable)

- FIFO Overflow

- Receive Timeout

- 2 Ports Configurable as Master or Slave

- I Port is Master Only

- Uses the SPI Boot ROM pins after startup

- **I**<sup>2</sup>**C**

- Standard I<sup>2</sup>C-compliant bus inference

- Dedicated open-drain pins supporting I<sup>2</sup>C Fast-mode

- Configurable as Master or Slave

- 16 word Transmit and Receive FIFOs

- Configurable Interrupt generation

- FIFO empty/full level programmable

- Note: Fast-Mode non-obstruct feature is not supported

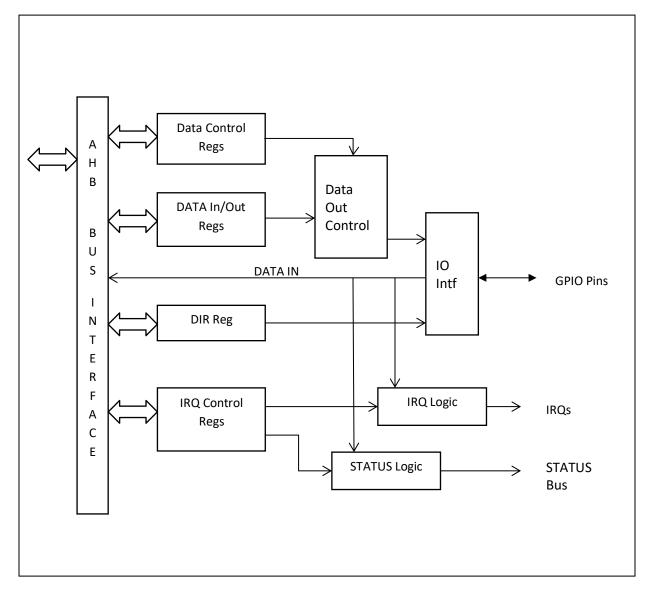

- o GPIO

- 2 GPIO Ports, Up to 56 pins total

- 32-bit port A

- 24-bit port B

- Configurable direction control of individual bits

- Bit level mask register allows single instruction setting or clearing of any bits in one port.

- Configurable interrupt detect on individual bits

- Level or Edge sensitive

- Configurable Pulse mode on individual bits

- Configurable (0-3) cycle delay on individual bits

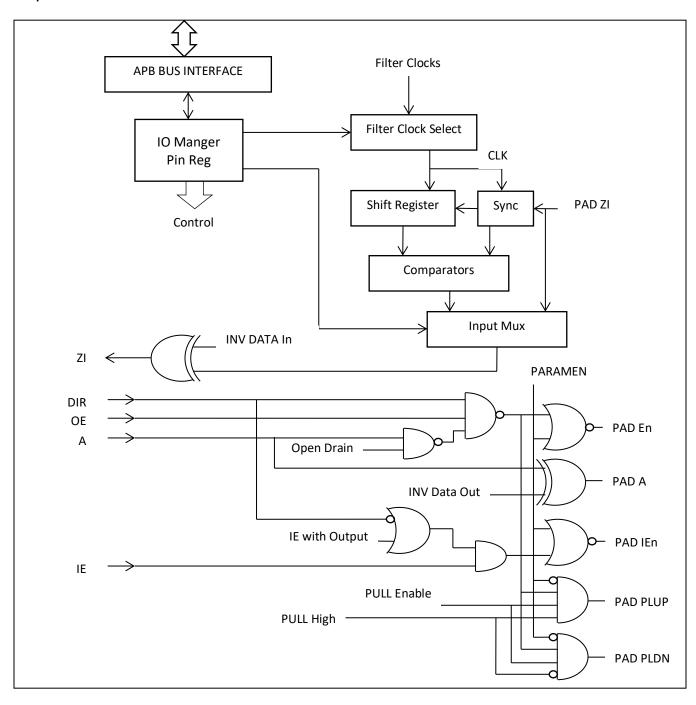

- IO Configuration

- Manages GPIO/SPI/UART IO configurations:

- Glitch filters

- Pull-up/Pull-down

- Signal inversion

- Pseudo open-drain

- Maps Timer, SPI and UART blocks to specific pins

- Counters/Timers

- 24 Counter/Timers

- Advanced trigger modes

- Start/Stop based on other Counter/Timers or GPIO signals

- Multiple trigger sources

- Configurable output event

- One cycle zero detect

- Active mode

- Divide by 2

- PWM compare

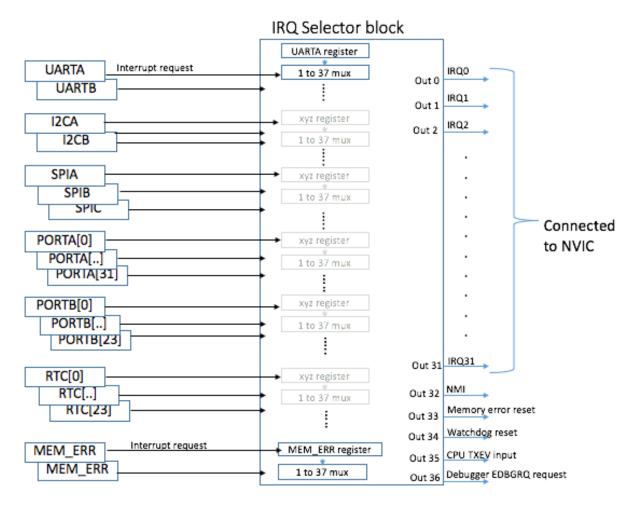

- Interrupt Select

- Maps >100 possible interrupt sources to the 32 NVIC inputs

- Configurable source for alternate Interrupts

- NMI

- Watchdog Reset

- Memory Error Reset

- Processor Receive Event

- System Configuration

- Memory Control

- Data memory clear on reset

- Code memory reload on reset

- Code memory write protect

- Code/Data memory Scrub rate (VA10820 Only)

- Code/Data memory error injection for testing (VA10820 Only)

- Code/Data memory SBE/MBE counters (VA10820 Only)

- Code/Data memory SBE/MBE Interrupt control (VA10820 Only)

- EDAC Syndrome calculation support (VA10820 Only)

- Register for Scrub rate control. (Performs EDAC read sequentially through both data and code memory.) (VA10820 Only)

- GPIO Glitch Filter rate control

- Peripheral Configuration

- Enable/Disable/Reset individual peripherals

- JTAG

- 2 Serial Controllers on same pins

- M0 Debug Controller

- Provides access to M0 Debug port

- VORAGO Controller

- Provides standard boundary scan

- Provides BIST access to memories

- Provides eFuse access

- Provides Test mode access

- Scan

- IDDQ

- I/O Parametric

- Configuration of Boot sequence

- Configuration of Memory Margin

- eFuse

- 32-bit Unique ID Number Support

- Custom part configuration information

- SPI ROM interface Delay, Speed, Size, Checking

- Multiple reconfiguration support (limited to 30 times)

### 2.2 Block Diagram

Figure 1 - Chip Block Diagram

### 2.3 Memory Map

The processor chip contains several memory areas shown below:

|                       | ] OxFFFF FFFF ┌ |                     | Ox400F FFFF                        |

|-----------------------|-----------------|---------------------|------------------------------------|

| Processor Reserved    | 0xE000 0000     | Reserved            | 0                                  |

| Reserved              |                 | Reserved            | 0x400F 000                         |

| Reserved              | 0x7000 0000     | I2C (2)             | 0x4006 200                         |

| Reserved              | 0x6000 0000     | Reserved            | 0x4006 000                         |

|                       | 0x5000 2000     |                     | 0x4005 300                         |

| AHB Peripheral PORTB  | 0x5000 1000     | SPI (3)             | 0x4005 000                         |

| AHB Peripheral PORTA  | 0x5000 0000     | Reserved            | 0x4004 200                         |

| Reserved              |                 | UART (2)            | 0,4004 200                         |

| APB Peripherals       | 0x4010 0000     | Reserved            | 0x4004 000                         |

| Reserved              | 0x4000 0000     | Counter/Timers (24) | 0x4003 800                         |

| Reserved              | 0x2000 0000     | Reserved            | 0x4002 000                         |

| 32k on-chip Data RAM  | 0x1000 8000     | Utility             | 0x4000 400                         |

| Reserved              | 0x1000 0000     |                     | 0x4000 300                         |

|                       | 0x0002 0000     | IO Config           | 0x4000 200                         |

| 128k on-chip Code RAM | 0x0000 0000     | IRQ Selector        | 0x4000 100                         |

|                       |                 | System Config       | $\int_{0x4000\ 000}^{0x4000\ 100}$ |

### 2.4 Power-Up Sequence

The VA10800/VA10820 auto-detects the Power-Up condition and begins operations by loading the internal code memory from an external Serial Peripheral Interface (SPI) based memory. After loading the code memory, the processor follows a normal ARM® Cortex®-M0 start sequence.

The Power-Up sequence is triggered by the internal Power-On-Reset detection logic and controlled by the internal nominal 1MHz oscillator. When the Power-Up condition is triggered, the primary internal logic (and the ARM® Cortex®-M0 processor) is held in reset until the Power-Up sequence completes. This sequence consists of the following steps:

- 1. 1ms delay from 1000 cycles of the nominal 1MHz oscillator (this allows VDD/VDDIO to reach higher levels)

- 2. Read internal eFuse to get the configuration data.

- 3. Timed delay based on eFuse configuration data and the nominal 1MHz oscillator.

- 4. Release of reset to the SPI boot controller. This begins the process of loading the internal code memory with data from the external SPI boot memory. The memory is read starting at address 0, in blocks of 128 bytes. Some aspects of this SPI based boot process are customizable (such as SPI speed, SPI latency, boot memory size, etc.); these are documented in the JTAG and eFuse sections.

- 5. Release of reset to the ARM® Cortex®-M0 processor. This begins the execution of code by the processor.

The EXTRESETn pin can also be used to delay the Power-Up Sequence. If EXTRESETn is active (low) at any time during the initial 1ms delay, the Power-Up sequence is stalled until EXTRESETn is inactive (high).

In addition to loading the code memory, the Power-Up reset sequence (step 4) will initialize the data memory to all zero values. This allows correct error-detect and correct (EDAC) syndromes to be generated for all memory data.

The CLK pin must be valid starting at step 4. Valid clock means stable values (below  $V_{IL}$  or above  $V_{IH}$ ) and meeting the minimum Clock high and low times. This allows the clock to be off as long as the level is valid. Steps 4 and 5 clock source is the CLK pin. If the CLK pin, does not have a valid input, steps 4 and 5 will not occur and no code will be executed.

### 2.4.1 Power-Up and Reset Behavior of pins

This section describes the Power-Up and Reset behavior of the GPIO pins on the device.

- At Power-up, an internal SYNC\_PORESET signal is asserted asynchronously (without a clock required). For all other reset events the internal SYNC\_PORESET signal is asserted synchronously to the clock.

- The SYNC\_PORESET signal directly asserts the internal HRESET signal. This signal synchronously resets the processor and peripherals.

- The IO interface unit places all the GPIO pins in the high-Z state while HRESET is active.

- The HRESET is de-asserted after loading the program code from external memory when the processor starts its boot sequence.

- Processor boot code can then configure the pins as needed by the peripheral control registers.

### 2.5 Other Resets

In addition to the Power-Up reset, the device can be reset from other events:

- EXTRESETn pin

- SYSRESETREQ from software

- Hardware events configured by IRQ Selector Peripheral or the System Controller Peripheral:

- Processor Lockup

- Watchdog Timer

- Memory Errors (Single or Multibit errors from the EDAC memory controller)

Based on previous software configuration (in the RST\_CNTL\_ROM and RST\_CNTRL\_RAM registers), these reset events may or may not re-initialization the memories similar to the Power-Up reset sequence.

### 2.6 $I^2C$ pins

The VA10800/VA10820 contains 2 sets of dedicated I<sup>2</sup>C pins and related I<sup>2</sup>C controllers. Each controller can act as both an I<sup>2</sup>C master and an I<sup>2</sup>C slave simultaneously. These interfaces are capable of operating at up to 100 kbits/s in Standard-mode, and up to 400 kbits/s in Fast-mode.

Note, that due to the ESD protection used in the HARDSIL<sup>TM</sup> process, the device does not meet the non-obstruct feature of I<sup>2</sup>C Fast-Mode when this device is powered off. If this non-obstruct feature is required in a system using this part, it will need to be implemented external to the device.

# 3 ARM<sup>®</sup> Cortex<sup>®</sup>-M0 processor

Primary documentation on the Cortex<sup>®</sup>-M0 processor can be found in the ARM<sup>®</sup> Documents:

- Cortex<sup>®</sup>-M0 Generic User Guide

- Cortex<sup>®</sup>-M0 Technical Reference Manual

The included ARM<sup>®</sup> Cortex<sup>®</sup>-M0 processor is configures as follows:

- All memory access is in little-endian format

- Code Memory is at addresses: 0x0000000-0x0001FFFF

- Data Memory is at addresses: 0x1000000-0x10007FFF

- Nested Vectored Interrupt Controller (NVIC) with 32 interrupts

- Assignment of interrupts is based on the IRQ Selector Peripheral

- Low latency IRQ mode

- System timer (SysTick) is present

- The SysTick Calibration (SYST\_CALIB) registers reports: 0xC000000, which indicates:

- NOREF no alternative reference clock source

- SKEW CLK does not guarantee an exact multiple of 10ms

- Single cycle multiple is present

- Processor sleep mode supported

- Includes clock gating for reduced power

- Full debug port is present

- Using JTAG interface

- 4 breakpoint comparators

- 2 data watchpoint comparators

- Processor External Event Inputs signal available from IRQ Selector Peripheral

- System reset request (SYSRESETREQ bit in the AIRCR register) will issue a system reset request.

- Wake-up interrupt controller (WIC) is not present

- Deep sleep with power disabled is not supported.

## **4** Peripherals

### 4.1 System Configuration Peripheral (Software label = SYSCONFIG)

The system configuration peripheral contains registers that monitor and configure system wide operation.

| Name          | Access | Address<br>offset | Description                          | Reset value    |

|---------------|--------|-------------------|--------------------------------------|----------------|

| RST_STAT      | RW     | 0x000             | System Reset Status<br>Register      | See Details    |

| RST_CNTL_ROM  | RW     | 0x004             | System Reset Control ROM<br>Register | 0x0000<br>003F |

| RST_CNTL_RAM  | RW     | 0x008             | System Reset Control RAM<br>Register | 0x0000<br>003F |

| ROM_PROT      | RW     | 0x00C             | ROM Memory Protection                | 0x0000<br>0000 |

| ROM_SCRUB     | RW     | 0x010             | ROM Scrub Period                     | 0x0000<br>0000 |

| RAM_SCRUB     | RW     | 0x014             | RAM Scrub Period                     | 0x0000<br>0000 |

| ROM_TRAP_ADDR | RW     | 0x018             | ROM EDAC Trap Address                | 0x0000<br>0000 |

| ROM_TRAP_SYND | RW     | 0x01c             | RAM EDAC Trap Syndrome               | 0x0000<br>0000 |

| RAM_TRAP_ADDR | RW     | 0x020             | RAM EDAC Trap Address                | 0x0000<br>0000 |

| RAM_TRAP_SYND | RW     | 0x024             | RAM EDAC Trap Syndrome               | 0x0000<br>0000 |

| IRQ_ENB       | RW     | 0x028             | Enable IRQs                          | 0x0000<br>0000 |

| IRQ_RAW       | R      | 0x02c             | Raw IRQ Status                       | -              |

| IRQ_END       | R      | 0x030             | Enabled IRQ Status                   | -              |

| IRQ_CLR       | W      | 0x034             | Clear IRQ Status                     | -              |

| RAM_SBE       | RW     | 0x038             | Count of RAM SBE Errors              | 0x0000<br>0000 |

| RAM_MBE       | RW     | 0x03c             | Count of RAM MBE Errors              | 0x0000<br>0000 |

| ROM_SBE       | RW     | 0x040             | Count of ROM SBE Errors              | 0x0000<br>0000 |

| Table 1 - Syst | em Configuratio | n Peripheral Registers |

|----------------|-----------------|------------------------|

|----------------|-----------------|------------------------|

| ROM_MBE                                 | RW | 0x044      | Count of ROM MBE Errors               | 0x0000<br>0000   |

|-----------------------------------------|----|------------|---------------------------------------|------------------|

| IOCONFIG_CLKDIV0                        | R  | 0x048      | IO Filter Clock 0 Divide              | 0x0000           |

|                                         |    |            | value                                 | 0000             |

| IOCONFIG_CLKDIV1                        | RW | 0x04c      | IO Filter Clock 1 Divide              | 0x0000           |

|                                         |    |            | value                                 | 0000             |

| IOCONFIG_CLKDIV2                        | RW | 0x050      | IO Filter Clock 2 Divide              | 0x0000           |

|                                         |    |            | value                                 | 0000             |

| IOCONFIG_CLKDIV3                        | RW | 0x054      | IO Filter Clock 3 Divide              | 0x0000           |

|                                         |    |            | value                                 | 0000             |

| IOCONFIG_CLKDIV4                        | RW | 0x058      | IO Filter Clock 4 Divide              | 0x0000           |

|                                         |    |            | value                                 | 0000             |

| IOCONFIG_CLKDIV5                        | RW | 0x05c      | IO Filter Clock 5 Divide              | 0x0000           |

|                                         |    |            | value                                 | 0000             |

| IOCONFIG_CLKDIV6                        | RW | 0x060      | IO Filter Clock 6 Divide              | 0x0000           |

| _                                       |    |            | value                                 | 0000             |

| IOCONFIG_CLKDIV7                        | RW | 0x064      | IO Filter Clock 7 Divide              | 0x0000           |

|                                         |    |            | value                                 | 0000             |

| ROM_RETRIES                             | RO | 0x068      | ROM Boot Retry Count                  | 0x0000           |

|                                         |    |            | · · · · · · · · · · · · · · · · · · · | 0000             |

| REFRESH_CONFIG                          | RW | 0x06c      | Register Refresh Rate                 | 0x0000           |

|                                         |    |            |                                       | 0000             |

| TIM_RESETS                              | RW | 0x070      | TIM Reset Control                     | 0xFFFF           |

|                                         |    |            |                                       | FFFF             |

| TIM_CLK_ENABLES                         | RW | 0x074      | TIM Clock Enable Control              | 0x0000           |

|                                         |    |            |                                       | 0000             |

| PERIPHERAL_RESET                        | RW | 0x078      | Peripheral Reset Control              | <b>OxFFFF</b>    |

| · - · · · · · · · · · · · · · · · · · · |    |            |                                       | FFFF             |

| PERIPHERAL_CLK_ENABLES                  | RW | 0x07c      | Peripheral Clock Enable               | 0x0000           |

|                                         |    |            | Control                               | 0000             |

| LOCKUP_RESET                            | RW | 0x080      | Lockup Reset Enable                   | 0x0000           |

|                                         |    |            |                                       | 0001             |

|                                         |    | 0x084      | Reserved                              | -                |

|                                         |    | _          |                                       |                  |

|                                         |    | -<br>0×FEC |                                       |                  |

| EF_CONFIG                               | RO | 0xFF0      | eFuse Config Register                 | -                |

| EF_ID                                   | RO | 0xFF4      | eFuse ID Register                     | +                |

| PROCID                                  | RO | 0xFF8      | Processor ID Register                 | -<br>See Details |

| PERID                                   | RO | 0xFFC      | Peripheral ID Register                | 0x0180           |

|                                         | KU | UXFEC      |                                       | 07e1             |

|                                         |    |            |                                       | 0/61             |

#### 4.1.1 RST\_STAT Register

The system reset status register reports the source of the last system reset (including Power On Reset events). Multiple bits may be set if multiple resets were asserted at the same time. Bits are set in this registers by reset events. Bits are cleared by writing to this register.

| Bit  | Symbol    | Description                             |

|------|-----------|-----------------------------------------|

| 0    | POR       | Power On Reset                          |

| 1    | EXTRST    | External Reset                          |

| 2    | SYSRSTREQ | SYSRESETREQ from processor via software |

| 3    | LOCKUP    | System LOCKUP asserted                  |

| 4    | WATCHDOG  | Watchdog Reset asserted                 |

| 5    | MEMERR    | Memory Error Reset asserted             |

| 31:6 | Reserved  | Reserved, Reads as O                    |

#### 4.1.2 RST\_CNTL\_ROM Register

The system reset ROM control register controls which reset sources cause the Code RAM (ROM) to be reloaded from the external SPI ROM at reset. A one in any bit enables the given reset source. This register is only reset by a Power-On-Reset.

| Bit  | Symbol    | Description                                 | Power-on-<br>Reset<br>value |

|------|-----------|---------------------------------------------|-----------------------------|

| 0    | POR       | Power On Reset (This bit is read-only as 1) | 1                           |

| 1    | EXTRST    | External Reset                              | 1                           |

| 2    | SYSRSTREQ | SYSRESETREQ from processor via software     | 1                           |

| 3    | LOCKUP    | System LOCKUP asserted                      | 1                           |

| 4    | WATCHDOG  | Watchdog Reset asserted                     | 1                           |

| 5    | MEMERR    | Memory Error Reset asserted                 | 1                           |

| 31:6 | Reserved  | Reserved, Reads as O                        |                             |

#### 4.1.3 RST\_CNTL\_RAM Register

The system reset RAM control register controls which reset sources cause the Data RAM to be cleared on reset. A one in any bit enables the given reset source. This register is only reset by a Power-On-Reset.

| Bit | Symbol    | Description                             | Power-on-<br>Reset<br>value |

|-----|-----------|-----------------------------------------|-----------------------------|

| 0   | POR       | Power On Reset (This bit is always 1)   | 1                           |

| 1   | EXTRST    | External Reset                          | 1                           |

| 2   | SYSRSTREQ | SYSRESETREQ from processor via software | 1                           |

### VA10800/VA10820

| 3    | LOCKUP   | System LOCKUP asserted      | 1 |

|------|----------|-----------------------------|---|

| 4    | WATCHDOG | Watchdog Reset asserted     | 1 |

| 5    | MEMERR   | Memory Error Reset asserted | 1 |

| 31:6 | Reserved | Reserved, Reads as O        |   |

#### 4.1.4 ROM\_PROT Register

The ROM memory protection register controls write access to the CODE RAM. If a write access is attempted to the CODE RAM while it is write protected an access fault will be generated.

| Bit  | Symbol   | Value | Description                 | Reset<br>value |

|------|----------|-------|-----------------------------|----------------|

| 0    | WREN     |       | ROM Write Enable            | 0              |

|      |          | 0     | Code RAM is write protected |                |

|      |          | 1     | Code RAM is writable        |                |

| 31:1 | Reserved |       | Reserved, Reads as O        |                |

#### 4.1.5 ROM\_SCRUB Register

The ROM scrub register configures the background scrub rate for the Code RAM (ROM). A zero value disables the background scrub. A non-zero value sets the reset value for the scrub counter. When the counter reaches zero, it is restarted with the configured value, and a scrub request is issued. Each scrub request checks a single 32-bit memory word, and increments a scrub address register.

| Bit | Symbol | Description | Res |

|-----|--------|-------------|-----|

|     | _      |             |     |

Note that the scrub controller does not exist in the VA10800 version.

| Bit   | Symbol   | Description                            | Reset<br>value |

|-------|----------|----------------------------------------|----------------|

| 23:0  | VALUE    | Scrub Counter Reset value              | 0              |

| 30:24 | Reserved | Reserved, reads as 0                   |                |

| 31    | RESET    | Write-Only bit, writing a 1 resets the | 0              |

|       |          | counter                                |                |

#### 4.1.6 RAM\_SCRUB Register

The RAM scrub register configures the background scrub rate for the Data RAM. A zero value disables the background scrub. A non-zero value sets the reset value for the scrub counter. When the counter reaches zero, it is restarted with the configured value, and a scrub

request is issued. Each scrub request checks a single 32-bit memory word, and increments a scrub address register.

| Bit   | Symbol   | Description                                    | Reset<br>value |

|-------|----------|------------------------------------------------|----------------|

| 23:0  | VALUE    | Scrub Counter Reset value                      | 0              |

| 30:24 | Reserved | Reserved, reads as 0                           |                |

| 31    | RESET    | Write-Only bit, writing a 1 resets the counter | 0              |

Note that the scrub controller does not exist in the VA10800 version.

### 4.1.7 ROM\_TRAP\_ADDR Register

The ROM EDAC TRAP ADDRESS register along with the ROM EDAC TRAP SYND register provides a way to write bad EDAC data to the Code RAM (ROM) for testing purposes. When TRAP is ENABLEd and a write operation to the configured memory address is requested, then the ROM EDAC TRAP SYND register is used instead of the normal computed Syndrome bits. Note that since memory is configured as a 32-bit word, the lower 2 address bits are not used in the compare. Also, only those address bits that access the Memory are compared.

Note that EDAC is not supported in the VA10800 version.

| Bit  | Symbol   | Description                 | Reset<br>value |

|------|----------|-----------------------------|----------------|

| 1:0  | Reserved | Reserved                    | 0              |

| 30:2 | ADDR     | Address bits for TRAP match | 0              |

| 31   | ENABLE   | Enable TRAP mode            | 0              |

#### 4.1.8 ROM\_TRAP\_SYND Register

The ROM EDAC TRAP ADDRESS register along with the ROM EDAC TRAP SYND register provides a way to write bad EDAC data to the Code RAM (ROM) for testing purposes (See ROM\_TRAP\_ADDR Register description).

| Bit   | Symbol   | Description                        | Reset<br>value |

|-------|----------|------------------------------------|----------------|

| 4:0   | SYND0    | 4 bit syndrome for data bits 7:0   | 0              |

| 9:5   | SYND1    | 4 bit syndrome for data bits 15:8  | 0              |

| 14:10 | SYND2    | 4 bit syndrome for data bits 23:16 | 0              |

| 19:15 | SYND3    | 4 bit syndrome for data bits 31:24 | 0              |

| 31:20 | Reserved | Reserved, Reads as O               | 0              |

### 4.1.9 RAM\_TRAP\_ADDR Register

The RAM EDAC TRAP ADDRESS register along with the RAM EDAC TRAP SYND register provides a way to write bad EDAC data to the Data RAM (RAM) for testing purposes. When TRAP is ENABLEd and a write operation to the configured memory address is requested, then the RAM EDAC TRAP SYND register is used instead of the normal computed Syndrome bits. Note that since memory is configured as a 32-bit word, the lower 2 address bits are not used in the compare. Also, only those address bits that access the Memory are compared.

Note that EDAC is not supported in the VA10800 version.

| Bit  | Symbol   | Description                 | Reset<br>value |

|------|----------|-----------------------------|----------------|

| 1:0  | Reserved | Reserved                    | 0              |

| 30:2 | ADDR     | Address bits for TRAP match | 0              |

| 31   | ENABLE   | Enable TRAP mode            | 0              |

#### 4.1.10 RAM\_TRAP\_SYND Register

The RAM EDAC TRAP ADDRESS register along with the RAM EDAC TRAP SYND register provides a way to write bad EDAC data to the Data RAM (RAM) for testing purposes (See RAM\_TRAP\_ADDR Register description).

| Bit   | Symbol | Description                        | Reset<br>value |

|-------|--------|------------------------------------|----------------|

| 4:0   | SYND0  | 4 bit syndrome for data bits 7:0   | 0              |

| 9:5   | SYND1  | 4 bit syndrome for data bits 15:8  | 0              |

| 14:10 | SYND2  | 4 bit syndrome for data bits 23:16 | 0              |

| 19:15 | SYND3  | 4 bit syndrome for data bits 31:24 | 0              |

| 31:20 | ENABLE | Reserved, Reads as O               | 0              |

#### 4.1.11 IRQ\_ENB Register

The IRQ enable register configures which EDAC (Error Detect And Correct) sources will trigger Interrupts. Either the Data RAM or the Code RAM (ROM) can generate a single-bit or multi-bit error signal. This register is only reset by a Power-On-Reset.

Note that EDAC is not supported in the VA10800 version, so these interrupt sources do not exist in that version.

| Bit | Symbol | Description                           | Power-on- |

|-----|--------|---------------------------------------|-----------|

|     |        |                                       | Reset     |

|     |        |                                       | value     |

| 0   | RAMSBE | Enable from Data RAM single-bit error | 0         |

## VA10800/VA10820

| 1    | RAMMBE   | Enable from Data RAM multi-bit error  | 0 |

|------|----------|---------------------------------------|---|

| 2    | ROMSBE   | Enable from Code RAM (ROM) single-bit | 0 |

|      |          | error                                 |   |

| 3    | ROMMBE   | Enable from Code RAM (ROM) multi-bit  | 0 |

|      |          | error                                 |   |

| 31:4 | Reserved | Reserved, Reads as O                  |   |

#### 4.1.12 IRQ\_RAW Register

The IRQ raw status register is a read-only register that reports raw status of the IRQ sources. This is the value before the enable is applied.

| Bit  | Symbol   | Description                                 | Reset<br>value |

|------|----------|---------------------------------------------|----------------|

| 0    | RAMSBE   | IRQ from Data RAM single-bit error          | 0              |

| 1    | RAMMBE   | IRQ from Data RAM multi-bit error           | 0              |

| 2    | ROMSBE   | IRQ from Code RAM (ROM) single-bit<br>error | 0              |

| 3    | ROMMBE   | IRQ from Code RAM (ROM) multi-bit error     | 0              |

| 31:4 | Reserved | Reserved, Reads as O                        |                |

#### 4.1.13 IRQ\_END Register

The IRQ ENableD status register is a read-only register that reports enabled status of the IRQ sources. This is the value after the enable is applied.

| Bit  | Symbol   | Description                                 | Reset<br>value |

|------|----------|---------------------------------------------|----------------|

| 0    | RAMSBE   | IRQ from Data RAM single-bit error          | 0              |

| 1    | RAMMBE   | IRQ from Data RAM multi-bit error           | 0              |

| 2    | ROMSBE   | IRQ from Code RAM (ROM) single-bit<br>error | 0              |

| 3    | ROMMBE   | IRQ from Code RAM (ROM) multi-bit error     | 0              |

| 31:4 | Reserved | Reserved, Reads as O                        |                |

#### 4.1.14 IRQ\_CLR Register

The IRQ clear status register is a write-only register that clears IRQ sources. Writing a 1 in the given bits clears the given IRQ source (these do not need to be written back to 0).

| Bit | Symbol | Description                        |

|-----|--------|------------------------------------|

| 0   | RAMSBE | IRQ from Data RAM single-bit error |

| 1   | RAMMBE | IRQ from Data RAM multi-bit error  |

| 2   | ROMSBE | IRQ from Code RAM (ROM) single-bit |

|     |        | error                              |

| 3    | ROMMBE   | IRQ from Code RAM (ROM) multi-bit error |

|------|----------|-----------------------------------------|

| 31:4 | Reserved | Reserved                                |

#### 4.1.15 RAM\_SBE Register

The RAM SBE register provides a count of the number of Data RAM single-bit errors that have been generated. A zero value can be written to this register to clear it. This register is only reset by a Power-On-Reset.

| Bit   | Symbol   | Description          | Power-on-<br>Reset<br>value |

|-------|----------|----------------------|-----------------------------|

| 15:0  | COUNT    | Error Count          | 0                           |

| 31:16 | Reserved | Reserved, Reads as O |                             |

#### 4.1.16 RAM\_MBE Register

The RAM MBE register provides a count of the number of Data RAM multi-bit errors that have been generated. A zero value can be written to this register to clear it. This register is only reset by a Power-On-Reset.

| Bit   | Symbol   | Description          | Power-on-<br>Reset<br>value |

|-------|----------|----------------------|-----------------------------|

| 15:0  | COUNT    | Error Count          | 0                           |

| 31:16 | Reserved | Reserved, Reads as O |                             |

### 4.1.17 ROM\_SBE Register

The ROM SBE register provides a count of the number of Code RAM(ROM) single-bit errors that have been generated. A zero value can be written to this register to clear it. This register is only reset by a Power-On-Reset.

| Bit   | Symbol   | Description          | Power-on-<br>Reset<br>value |

|-------|----------|----------------------|-----------------------------|

| 15:0  | COUNT    | Error Count          | 0                           |

| 31:16 | Reserved | Reserved, Reads as 0 |                             |

#### 4.1.18 ROM\_MBE Register

The ROM MBE register provides a count of the number of Code RAM (ROM) multi-bit errors that have been generated. A zero value can be written to this register to clear it. This register is only reset by a Power-On-Reset.

| Bit   | Symbol   | Description          | Power-on-<br>Reset<br>value |

|-------|----------|----------------------|-----------------------------|

| 15:0  | COUNT    | Error Count          | 0                           |

| 31:16 | Reserved | Reserved, Reads as O |                             |

### 4.1.19 IOCONFIG\_CLKDIV0-7 Registers

The IOCONFIG0 to IOCONFIG7 registers provide access to the divide value used to generate the IO configuration filter clocks 0 through 7. These clocks can be used to filter glitches on the configurable IO pins or as cascade sources on the Timer/Counters. A zero value in a given register will disable the associated clock. A 1 value provides the system clock. A 2 value provides the system clock divided by 2. Note that IOCONFIGCLKDIV0 is read-only and has a fixed value of 0x0000 0001 (which is the system clock).

| Bit  | Symbol | Description                            | Reset value |

|------|--------|----------------------------------------|-------------|

| 31:0 | COUNT  | Clock divide value. 0 will disable the | 0x0000      |

|      |        | clock.                                 | 0000        |

|      |        |                                        |             |

### 4.1.20 ROM\_RETRIES Register

The ROM RETRIES register provides a count of the number of Code RAM (ROM) block retries that happened during the ROM code fetch on the ROM SPI port during the reset startup. This register is read only. If more than 255 retries happened, the count value will be 255.

| Bit  | Symbol   | Description          | Reset<br>value |

|------|----------|----------------------|----------------|

| 7:0  | COUNT    | Error Count          | 0              |

| 31:8 | Reserved | Reserved, Reads as O |                |

### 4.1.21 REFRESH\_CONFIG Register

The REFRESH CONFIG register provides control of the Register Refresh Rate. Registers are clock gated to reduce power; however, clock gating prevents TMR registers from self-correcting. To allow this self-correct, the registers are refreshed periodically. The REFRESH CONFIG register controls the refresh rate.

Note that the refresh controller does not exist in the VA10800 version.

| Bit  | Symbol   | Value | Description                                                                            | Reset<br>value |

|------|----------|-------|----------------------------------------------------------------------------------------|----------------|

| 15:0 | DIVCOUNT |       | This specifies the clock divided value<br>(plus 1) for the refresh rate. Registers are | 0x000f         |

### VA10800/VA10820

|       |          |       | clocked every (DIVCOUNT+1)*16<br>cycles. |     |

|-------|----------|-------|------------------------------------------|-----|

| 29:16 | Reserved |       | Reserved, Reads as O                     |     |

| 31:30 | TESTMODE |       | Special Test Mode configuration          | 0x0 |

|       |          | 00/01 | Normal                                   |     |

|       |          | 10    | Force refresh off                        |     |

|       |          | 11    | Force refresh on constantly              |     |

#### 4.1.22 TIM\_RESET Register

The TIM RESET register provides control of the resets to the Timer/Counters. Each bit controls the reset of a given TIM. The resets are active low, so setting a given bit to 0 will hold the related TIM in reset.

| Bit   | Symbol   | Description           | Reset<br>value |

|-------|----------|-----------------------|----------------|

| 23:0  | RESET[i] | Resetn of a given TIM | 0xffffff       |

| 31:24 | Reserved | Reserved, Reads as 1  | 0xff           |

#### 4.1.23 TIM\_CLK\_ENABLE Register

The TIM CLK ENABLE register provides control of the clock enables to the Timer/Counters. Each bit controls the clock enable signal of a given TIM. The clock enables are active high, so setting a given bit to 1 will enable the clock to a given TIM. When the given enable is 0, the related TIM will not normally be clocked (except by the refresh logic).

| Bit   | Symbol   | Description                 | Reset<br>value |

|-------|----------|-----------------------------|----------------|

| 23:0  | RESET[i] | Clock Enable of a given TIM | 0x000000       |

| 31:24 | Reserved | Reserved, Reads as O        | 0x00           |

#### 4.1.24 PERIPHERAL\_RESET Register

The PERIPHERAL RESET register provides control of the resets of selected peripherals. Each bit controls the reset of a given peripheral. The resets are active low, so setting a given bit to 0 will hold the related peripheral in reset.

| Bit | Symbol   | Description         | Reset<br>value |

|-----|----------|---------------------|----------------|

| 0   | PORTA    | Resetn of a PORTA   | 1              |

| 1   | PORTB    | Resetn of a PORTB   | 1              |

| 3:2 | Reserved | Reserved            | 3              |

| 6:4 | SPI[i]   | Resetn of SPI ports | 7              |

| 7   | Reserved | Reserved            | 3              |

### VA10800/VA10820

| 9:8   | UART[i]  | Resetn of UART ports             | 3      |

|-------|----------|----------------------------------|--------|

| 15:10 | Reserved | Reserved                         | 0x3f   |

| 17:16 | I2C[i]   | Resetn of I <sup>2</sup> C ports | 3      |

| 19:18 | Reserved | Reserved                         | 3      |

| 20    | SYSTEM   | Resetn of System Config          | 1      |

| 21    | IRQSEL   | Resetn of IRQ Selector           | 1      |

| 22    | IOCONFIG | Resetn of IO Config              | 1      |

| 23    | UTILITY  | Resetn of Utility Peripheral     | 1      |

| 24    | PORTIO   | Resetn of PORT IO interface      | 1      |

| 31:25 | Reserved | Reserved                         | 0xffff |

#### 4.1.25 PERIPHERAL\_CLK\_ENABLE Register

The PERIPHERAL CLK ENABLE register provides control of the clock enables of selected peripherals. Each bit controls the clock enable signal of a given peripheral. The clock enables are active high, so setting a given bit to 1 will enable the clock to a given peripheral. When the given enable is 0, the related peripheral will not normally be clocked. In VA10820 the peripherals are still clocked occasionally based on the REFRESH\_CONFIG register setting.

Note: For a peripheral to access any GPIO, both the peripheral and the IOCONFIG module clocks must be enabled.

| Bit   | Symbol   | Description                            | Reset<br>value |

|-------|----------|----------------------------------------|----------------|

| 0     | PORTA    | Clock Enable of PORTA                  | 0              |

| 1     | PORTB    | Clock Enable of PORTB                  | 0              |

| 3:2   | Reserved | Reserved                               | 0              |

| 6:4   | SPI[i]   | Clock Enable of SPI ports              | 0              |

| 7     | Reserved | Reserved                               | 0              |

| 9:8   | UART[i]  | Clock Enable of UART ports             | 0              |

| 15:10 | Reserved | Reserved                               | 0              |

| 17:16 | I2C[i]   | Clock Enable of I <sup>2</sup> C ports | 0              |

| 19:18 | Reserved | Reserved                               | 0              |

| 20    | Reserved | Reserved                               | 0              |

| 21    | IRQSEL   | Clock Enable of IRQ Selector           | 0              |

| 22    | IOCONFIG | Clock Enable of IO Configuration block | 0              |

| 23    | UTILITY  | Clock Enable of Utility                | 0              |

| 24    | GPIO     | Clock Enable of GPIO interface         | 0              |

| 31:25 | Reserved | Reserved                               | 0              |

#### 4.1.26 Lockup Reset Register

The Lockup reset register controls if the system is reset on a processor lockup event or not.

| Bit                                | Symbol                     | Value | Description                      | Reset<br>value |

|------------------------------------|----------------------------|-------|----------------------------------|----------------|

| 0                                  | 0 LREN Lockup Reset Enable |       | Lockup Reset Enable              | 1              |

|                                    |                            | 0     | Processor is not reset on lockup |                |

|                                    |                            | 1     | Processor is reset on lockup     |                |

| 31:1 Reserved Reserved, Reads as 0 |                            |       |                                  |                |

#### 4.1.27 EF\_CONFIG Register

This is a read-only register that returns the EF\_CONFIG value read from the eFuse block at boot time. Programming the eFuse configuration controls the BOOT parameters as defined in the below table. The eFuse contents can be modified by the user as detailed in section 5.3.

| Bit | Reset<br>State | Name            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|----------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1:0 | 0x1            | ROM_SPEED       | This value specifies the speed of ROM_SCK:<br>0 - CLK divide by 2 (@50MHz => 25MHz)<br>1 - CLK divide by 6 (@50MHz => 8.33MHz)<br>2 - CLK divide by 12 (@50MHz => 4.2MHz)<br>3 - CLK divide by 52 (@50MHz => 962kHz)                                                                                                                                                                                                                                               |